# University of Wollongong Research Online

University of Wollongong Thesis Collection

University of Wollongong Thesis Collections

1998

# Harmonic control techniques for inverters and adaptive active power filters

Ali Hazdian Varjani University of Wollongong

#### Recommended Citation

$Varjani, Ali\ Hazdian, Harmonic\ control\ techniques\ for\ inverters\ and\ adaptive\ active\ power\ filters, Doctor\ of\ Philosophy\ thesis,\ School\ of\ Electrical,\ Computer\ and\ Telecommunications\ Engineering,\ University\ of\ Wollongong,\ 1998.\ http://ro.uow.edu.au/theses/1949$

#### NOTE

This online version of the thesis may have different page formatting and pagination from the paper copy held in the University of Wollongong Library.

#### UNIVERSITY OF WOLLONGONG

#### **COPYRIGHT WARNING**

You may print or download ONE copy of this document for the purpose of your own research or study. The University does not authorise you to copy, communicate or otherwise make available electronically to any other person any copyright material contained on this site. You are reminded of the following:

Copyright owners are entitled to take legal action against persons who infringe their copyright. A reproduction of material that is protected by copyright may be a copyright infringement. A court may impose penalties and award damages in relation to offences and infringements relating to copyright material. Higher penalties may apply, and higher damages may be awarded, for offences and infringements involving the conversion of material into digital or electronic form.

# Harmonic Control Techniques for Inverters and Adaptive Active Power Filters

A thesis submitted in fulfilment of the requirements for the award of the degree of

## **DOCTOR OF PHILOSOPHY**

from

#### UNIVERSITY OF WOLLONGONG

By

Ali Yazdian Varjani, B.Sc, M.Eng (Hons.)

School of Electrical, Computer and Telecommunication Engineering

November, 1998

In the name of God, the merciful and compassionate

# Dedicated to my wife who was beside me during these hard years

and my mother

who first encouraged me to undertake postgraduate studies

# **DECLARATION**

| This is to certify that the work presented in this thesis was perfe  | ormed by me, unless  |

|----------------------------------------------------------------------|----------------------|

| specified otherwise, and no part of it has been submitted previously | for any other degree |

| to any other university or similar institution.                      |                      |

|                                                                      |                      |

|                                                                      |                      |

|                                                                      |                      |

|                                                                      |                      |

|                                                                      | Ali Yazdian Varjani  |

**ACKNOWLEDGMENTS**

I would like to express my gratitude to my supervisors Professor Joe Chicharo and

Dr Sarath Perera for their invaluable guidance and support throughout this research

work.

I wish also to thank the Ministry of Culture and Higher Education of Islamic Republic of

Iran (MCHE) for awarding me a research scholarship through which complete financial

support was provided.

The support of the Electricity Supply Association of Australia (ESAA) for funding this

project highly acknowledged. I would like to thank my friends Dr M. Tavasoli, Dr A.

Shahri, Dr A. Dastfan, Dr A. Jalilian, and Dr M. Kahani, for valuable tips, comments and

discussions. I also thanks Dr Philip Oganbana for his comments and discussions and

Ms B. Evans for her proofreading.

At last but not least, my deepest gratitude to my wife Monirossadat for her warm

supports, understanding and patiently taking upon on herself my share of the

responsibilities at home.

Ali Yazdian Varjani

V

## **ABSTRACT**

This thesis is concerned with the general issue of power quality. The specific areas of interest include harmonic distortion and its minimisation. In particular the thesis considers a PWM switching strategy which yields near optimal performance in terms of harmonic distortion as well as on-line harmonic detection mechanisms and adaptive active power filtering solutions.

For the purpose of load side harmonic reduction, a novel equal area based PWM (EAPWM) switching strategy is developed which is suitable for voltage source full bridge inverter applications. The objective of this strategy is to minimise both the harmonic distortion and the switching losses in the inverter. Switching losses in the inverter are minimised by developing a hybrid switching sequence. The harmonic distortion is minimised by adopting a technique which ensures that the PWM pulses are placed at appropriate positions of choice based on an equal area criterion so that their areas are better matched with the areas under the reference waveform.

The EAPWM technique is evaluated and its performance is compared with existing PWM techniques including natural and regular PWM switching strategies. The performance evaluation and comparison is based on the total harmonic distortion and maximum inverter fundamental output voltage. For a case where the ideal output waveform is sinusoidal it is shown through simulation that the proposed technique provides a PWM output with minimum harmonic distortion and maximum fundamental voltage.

The second issue addressed by the thesis is adaptive active power filtering. The objective is to develop an economical solution where a partial and flexible harmonic reduction technique is provided such that the established harmonic standards are satisfied. Partial and selective compensation of those individual harmonics which exceed the

recommended levels as set by regulatory bodies reduces the rating of active power filters thus leading to cost savings. This approach contrasts with existing techniques where the objective is to reduce all possible harmonic components to zero.

A new control strategy for active power filters that combines adaptive online harmonic estimation with partial and selective harmonic compensation schemes has been implemented within an integrated controller. To have an accurate online estimation of harmonic components, a new adaptive structure based on a combination of resonator filter bank and frequency demodulation frequency tracking is proposed.

Performance evaluation of the proposed technique for harmonic estimation for time-varying nonlinear load is carried out where the simulation results show that the proposed filter bank structure provides better performance when compared to widely used conventional technique such as short term Fourier transform. The proposed control strategy has been implemented using a digital signal processor. Experimental results from a laboratory prototype are presented showing steady state and transient performance. It is shown that the proposed harmonic estimation together with the flexible harmonic compensation scheme provides an efficient solution in reducing the power rating of the active power filter while limiting specific harmonics to desired levels of compensation.

## **AUTHOR'S PUBLICATIONS**

A. Yazdian-Varjani, B. S. P. Perera, and J. F. Chicharo, "A Centroid-Based PWM Switching Technique For Full-Bridge Inverter Applications," *IEEE Transactions on Power Electronics*, vol. 13, pp. 115-124, 1998.

A. Yazdian-Varjani, J. F. Chicharo, and B. S. P. Perera, "An Introduction to Wavelets in Power Quality Analysis," *Australasian Universities Power Engineering Conference*, *AUPEC'97*, Sydney, pp. 277-281, 1997.

A. Yazdian-Varjani, B. S. P. Perera, J. F. Chicharo, and M. T. Kilani, "An Equal Area Based Pulsewidth and Position Switching Strategy for Full-Bridge Inverter Applications," *Australasian Universities Power Engineering Conference*, *AUPEC'96*, Melbourne, pp. 143-149, 1996.

A. Yazdian-Varjani, B. S. P. Perera, J. F. Chicharo, and M. T. Kilani, "Sliding Measurement of Power System Harmonics," *Australasian Universities Power Engineering Conference, AUPEC'96*, Melbourne, pp. 293-299, 1996.

A. Yazdian-Varjani, J. F. Chicharo, and B. S. P. Perera, "Adaptive Active Power Filtering" Submitted for review to *IEEE Transactions on Power Electronics*, 1999.

# **CONTENTS**

| Chapter | 1: Preliminary                                                | 1  |

|---------|---------------------------------------------------------------|----|

|         | Introduction                                                  |    |

|         | Power System Harmonics                                        |    |

|         | 1.2.1 Harmonic Sources                                        | 2  |

|         | 1.2.2 Effects of Harmonic                                     | 2  |

|         | 1.2.3 Measurement of Harmonics 1.2.3.1 MEASUREMENT TECHNIQUES |    |

|         | 1.2.4 Standards on Harmonics                                  |    |

| 1.3     | Compensation of Harmonics                                     | 4  |

|         | 1.3.1 Harmonic Reduction Techniques                           | 4  |

|         | 1.3.2 Passive Power Filters                                   | 5  |

|         | 1.3.3 Active Power Filters (APF)                              | 6  |

|         | 1.3.3.1 PRINCIPLE OF ACTIVE POWER FILTER                      | 6  |

|         | 1.3.4 Power System Connection                                 | 7  |

|         | 1.3.4.1 Shunt Configurations                                  | 7  |

|         | 1.3.4.2 SERIES CONFIGURATIONS                                 | 8  |

|         | 1.3.4.3 HYBRID CONFIGURATIONS                                 | 8  |

|         | 1.3.5 Control Strategies                                      | 9  |

|         | 1.3.5.1 TIME DOMAIN APPROACHES                                | 9  |

|         | 1.3.5.2 PREDETERMINED HARMONIC CANCELLATION                   | 10 |

|         | 1.3.5.3 FREQUENCY DOMAIN APPROACHES                           | 10 |

|      | 1.4  | Thesis Objectives and Outline                               | .11   |

|------|------|-------------------------------------------------------------|-------|

|      |      | 1.4.1 Pulsewidth Modulation (PWM)                           | . 11  |

|      |      | 1.4.2 Adaptive Active Power Filter (AAPF)                   | . 11  |

|      |      | 1.4.2.1 HARMONIC ESTIMATION                                 | 12    |

|      |      | 1.4.2.2 Phase and Frequency Tracking                        | 12    |

|      |      | 1.4.2.3 SELECTIVE AND PARTIAL HARMONIC COMPENSATION SCHEMES | 5. 12 |

|      |      | 1.4.3 Contributions of the Thesis                           | . 13  |

|      |      | 1.4.3.1 NEW PWM SWITCHING STRATEGY                          | 13    |

|      |      | 1.4.3.2 HARMONIC ESTIMATION                                 |       |

|      |      | 1.4.3.3 ADAPTIVE ACTIVE POWER FILTER                        | 14    |

|      |      | 1.4.4 Thesis Outline                                        | . 14  |

| Chaj | pter | 2: Equal Area Based PWM Technique                           | .15   |

|      | 2.1  | Introduction                                                | .15   |

|      | 2.2  | Conventional PWM Techniques                                 | .16   |

|      |      | 2.2.1 Natural Sampling PWM Technique                        | . 16  |

|      |      | 2.2.2 Regular Sampling PWM Technique                        | 18    |

|      |      | 2.2.3 Equal Sampling PWM Technique (EST)                    | . 19  |

|      |      | 2.2.4 Centroid Based PWM Technique (CBT)                    | . 20  |

|      | 2.3  | Equal Area Based PWM Technique (EAPWM)                      | .22   |

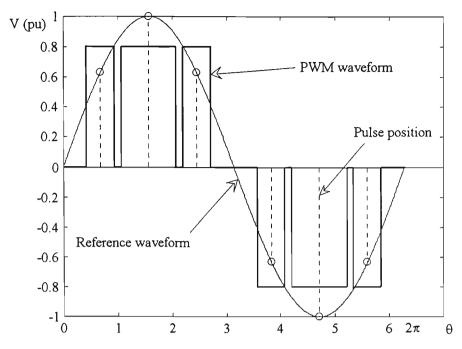

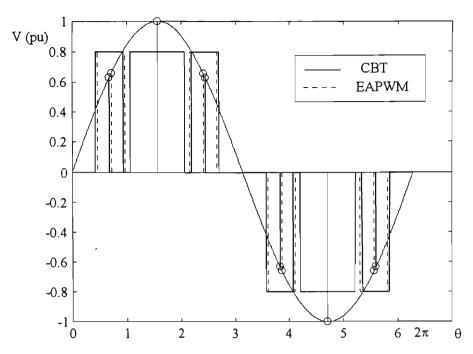

|      |      | 2.3.1 CBT and EAPWM Comparison                              | . 24  |

|      | 2.4  | Simulation and Performance Analysis                         | .26   |

|      |      | 2.4.1 Performance Evaluation                                | . 26  |

|      |      | 2.4.2 Simulation Results                                    | . 27  |

|      |      | 2.4.3 Comparison of CBT with Sinusoidal PWM Techniques      | . 30  |

|      |      | 2.4.4 Comparison of CBT and EAPWM                           | . 35  |

|      |      | 2.4.5 Predetermined Harmonic Cancellation                   | . 39  |

| 2.5     | Switching Sequence                                      | 43         |

|---------|---------------------------------------------------------|------------|

| 2.6     | Conclusions                                             | 44         |

| Chapter | 3: Harmonic Estimation                                  | 45         |

| 3.1     | Introduction                                            | 45         |

| 3.2     | Harmonic Estimation                                     | 46         |

|         | 3.2.1 Fourier Transform                                 | 47         |

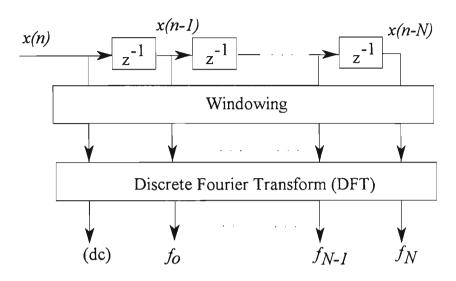

|         | 3.2.2 Short Term Fourier Transform                      | 48         |

| 3.3     | Filter Bank Based Harmonic Measurement                  | 49         |

|         | 3.3.1 Filter bank Structure                             | 50         |

|         | 3.3.2 Sliding Algorithm                                 | 54         |

| 3.4     | Frequency Estimation                                    | 55         |

|         | 3.4.1 Adaptive IIR Filtering                            | 55         |

|         | 3.4.1.1 GRADIENT DECENT ALGORITHMS                      | 57         |

|         | 3.4.2 Frequency Demodulation Technique                  | 58         |

|         | 3.4.2.1 LOW PASS FILTERING                              | 60         |

|         | 3.4.2.2 DECIMATION                                      | 61         |

| 3.5     | Simulation Results                                      | 61         |

|         | 3.5.1 Frequency Estimation.                             | 61         |

|         | 3.5.1.1 ADAPTIVE IIR FILTER                             | 62         |

|         | 3.5.1.2 FM DEMODULATION (FMD)                           | 63         |

|         | 3.5.2 Harmonic Estimation                               | 65         |

|         | 3.5.2.1 SHORT TERM FOURIER TRANSFORM                    | 66         |

|         | 3.5.2.2 FILTER BANK HARMONIC ESTIMATION AND MEASUREMENT | 68         |

|         | 3.5.2.3 COMPUTATIONAL BURDEN                            | 71         |

| 3.6     | Conclusion                                              | <b>7</b> 1 |

| Chapter | 4: Active Power Filter Implementation            | 73 |

|---------|--------------------------------------------------|----|

| 4.1     | Introduction                                     | 73 |

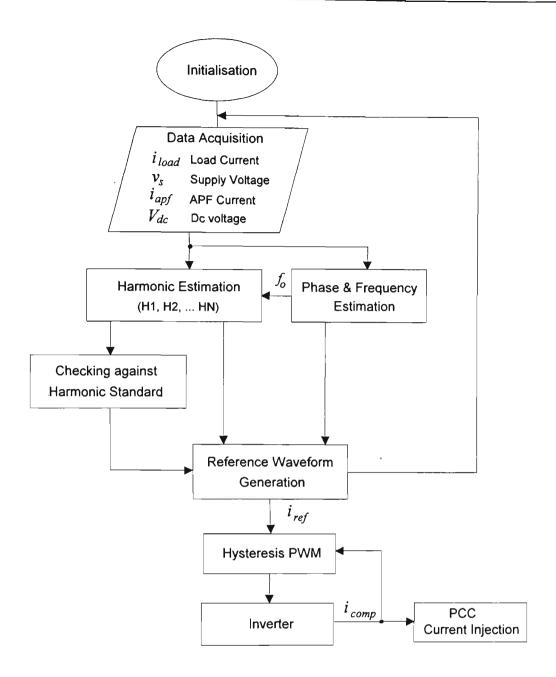

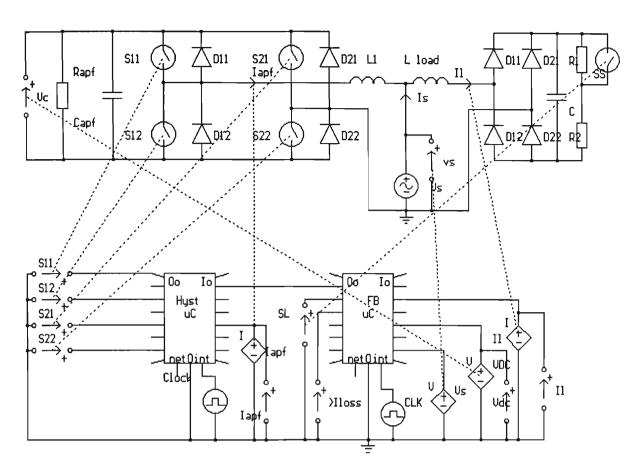

| 4.2     | Control Strategy                                 | 75 |

|         | 4.2.1 Data Acquisition                           | 75 |

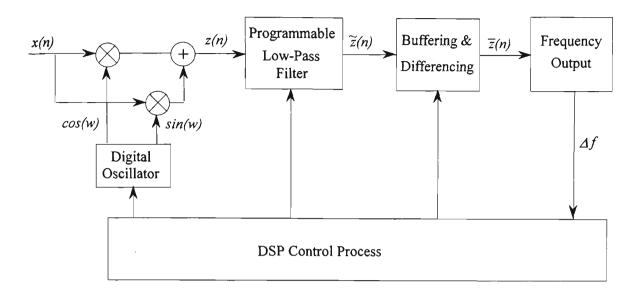

|         | 4.2.2 Frequency Tracking                         | 76 |

|         | 4.2.2.1 FIR FILTERING                            | 77 |

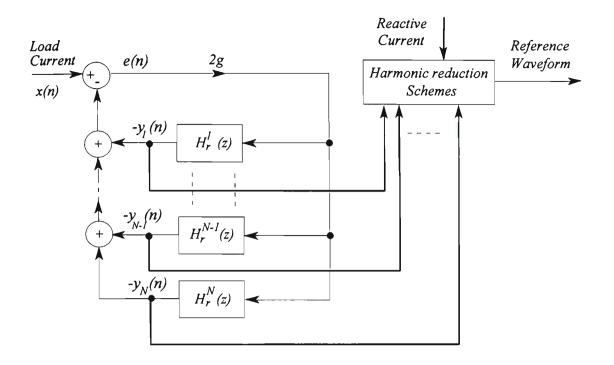

|         | 4.2.3 Harmonic Estimation and Prediction         | 78 |

|         | 4.2.3.1 HARMONIC ESTIMATION                      | 78 |

|         | 4.2.3.2 HARMONIC PREDICTION                      | 78 |

|         | 4.2.3.3 IIR FILTER BANK                          | 79 |

|         | 4.2.4 Active Power Filter Reference Waveform     | 80 |

|         | 4.2.4.1 POWER CALCULATION                        | 80 |

|         | 4.2.4.2 DC LINK VOLTAGE CONTROLLER               | 81 |

|         | 4.2.5 Harmonic Compensation Schemes              | 82 |

|         | 4.2.5.1 FULL COMPENSATION SCHEME                 | 82 |

|         | 4.2.5.2 SELECTIVE HARMONIC COMPENSATION SCHEMES  | 83 |

|         | 4.2.5.3 COMPENSATION BASED ON HARMONIC STANDARDS | 83 |

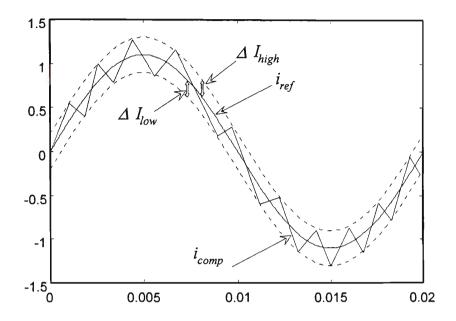

|         | 4.2.5.4 PWM WAVEFORM GENERATION                  | 84 |

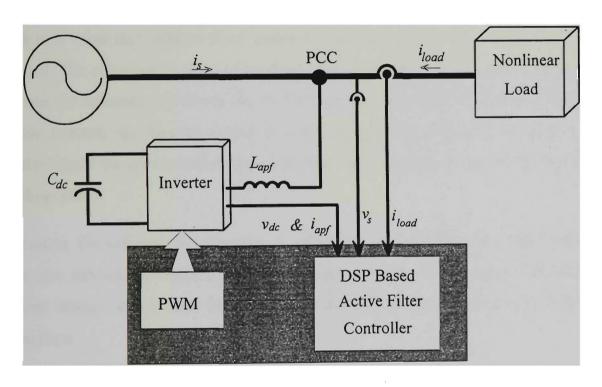

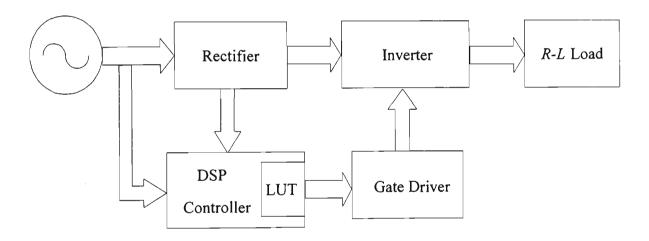

| 4.3     | Hardware Configuration                           | 85 |

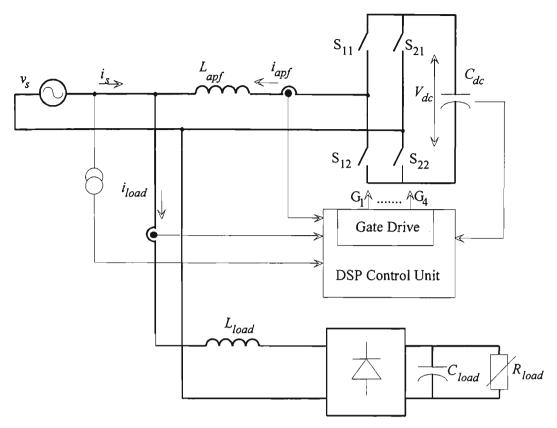

|         | 4.3.1 IGBT Voltage Source Inverter               | 86 |

|         | 4.3.1.1 ISOLATION INDUCTANCE                     | 86 |

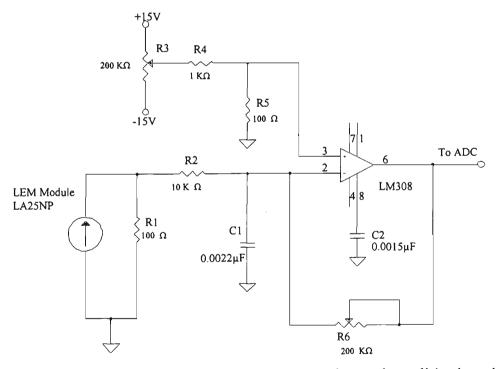

|         | 4.3.1.2 CURRENT SENSING                          | 87 |

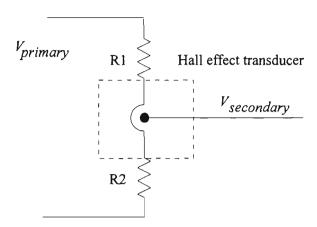

|         | 4.3.1.3 VOLTAGE SENSING                          | 87 |

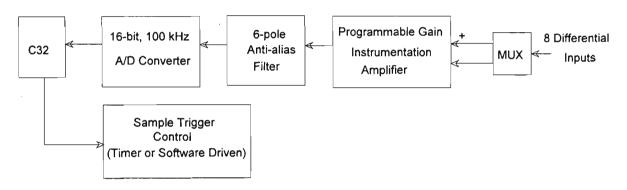

|         | 4.3.2 DSP Hardware                               | 88 |

|         | 4.3.2.1 DSP CONFIGURATION                        | 88 |

|         | 4.3.2.2 DATA ACQUISITION                         | 88 |

| 4.4     | Software Simulation                              | 89 |

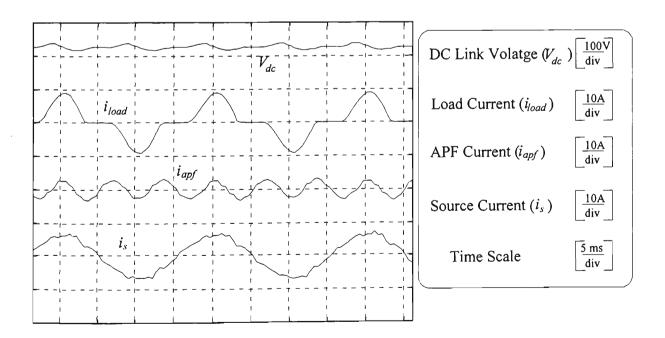

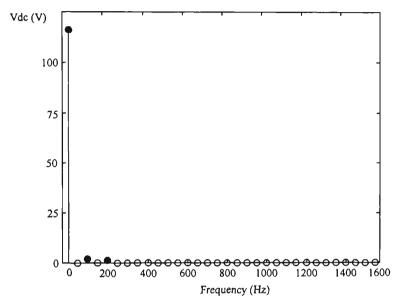

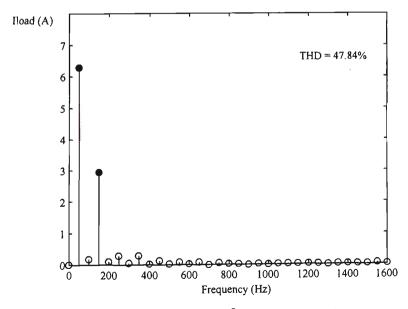

|         | 4.4.1 Steady State Condition.                    | 91 |

|         | 4.4.2 Transient Condition                        | 93 |

| 4.5     | Conclusions                                      | 94 |

| Chapter | 5: Experimental Results                                                          | 96  |

|---------|----------------------------------------------------------------------------------|-----|

| 5.1     | Introduction                                                                     | 96  |

|         | 5.1.1 Test Conditions                                                            | 97  |

| 5.2     | Equal Area Based PWM Technique (EAPWM)                                           | 97  |

|         | 5.2.1 PWM Operation.                                                             | 98  |

|         | 5.2.2 Harmonic Distortion                                                        | 101 |

| 5.3     | Harmonic and Frequency Estimation                                                | 103 |

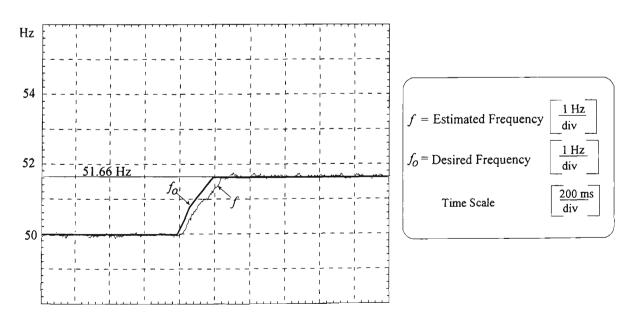

|         | 5.3.1 Frequency Estimation.                                                      | 103 |

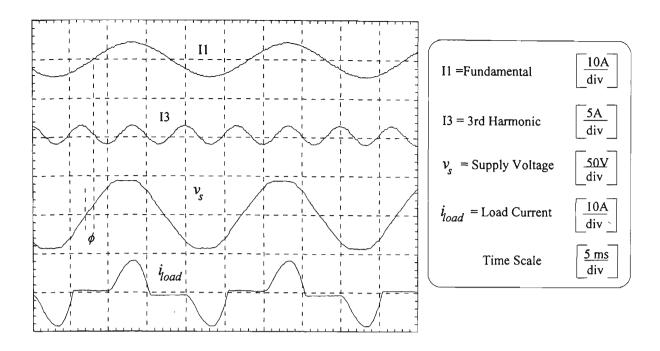

|         | 5.3.2 Harmonic Estimation with Filter Bank                                       | 104 |

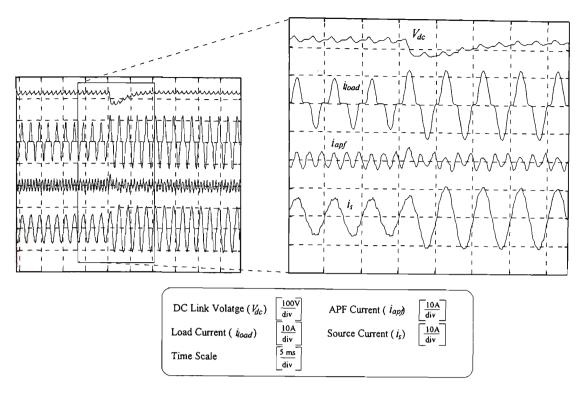

| 5.4     | Harmonic Compensation                                                            | 107 |

|         | 5.4.1 Full Harmonic Compensation                                                 | 107 |

|         | 5.4.2 Selective Compensation                                                     | 108 |

|         | 5.4.2.1 3 <sup>RD</sup> HARMONIC CANCELLATION                                    | 109 |

|         | 5.4.2.2 5 <sup>th</sup> HARMONIC CANCELLATION                                    | 110 |

|         | 5.4.2.3 3 <sup>RD</sup> AND 5 <sup>TH</sup> HARMONIC CANCELLATION                | 111 |

|         | 5.4.2.4 3 <sup>RD</sup> + 5 <sup>TH</sup> +7 <sup>TH</sup> HARMONIC CANCELLATION |     |

|         | 5.4.3 Compensation Based Harmonic Standards                                      | 115 |

|         | $5.4.3.1$ : $K_h^{std} = 5\%$                                                    | 115 |

|         | $5.4.3.2: K_h^{std} = 10\%$                                                      | 116 |

|         | 5.4.3.3: $K_h^{std} = 15\%$                                                      | 118 |

|         | $5.4.3.4: K_h^{std} = 20\%$                                                      | 119 |

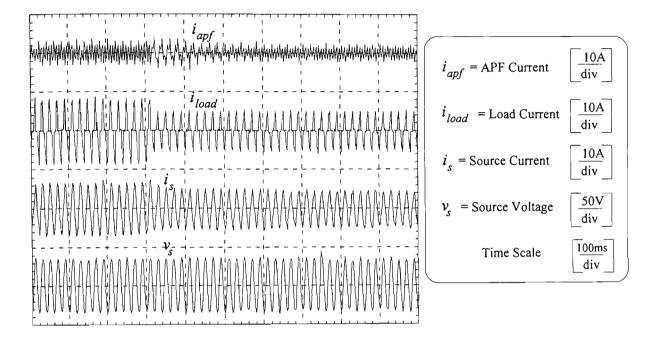

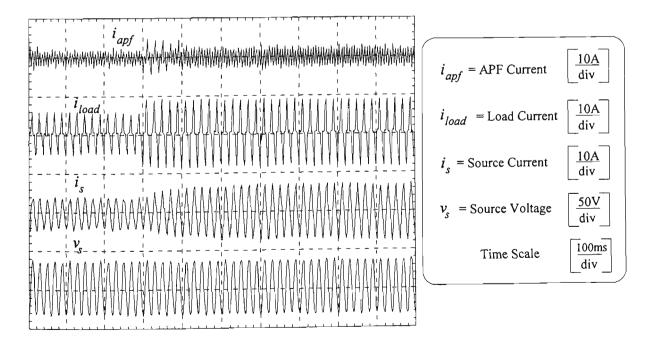

|         | 5.4.4 Transient Performance                                                      | 120 |

| 5.5     | Conclusion                                                                       | 122 |

| Chapter 6: |        | : (           | Conclusion                                        |     |

|------------|--------|---------------|---------------------------------------------------|-----|

| 6.         | .1 E   | Equal         | Area Based PWM Technique (EAPWM)                  | 124 |

| 6.         | .2 H   | Iarm          | onic Reduction                                    | 125 |

|            | 6      | .2.1 I        | nfinite Impulse Response (IIR) Filter Bank        | 125 |

|            | 6      | .2.2 <b>H</b> | Frequency Tracking                                | 125 |

|            | 6      | .2.3 I        | Harmonic Estimation                               | 126 |

|            | 6      | .2.4 I        | Harmonic Magnitude Calculation                    | 126 |

| 6.         | .3 A   | Active        | e Power Filter                                    | 127 |

| 6.         | .4 E   | Exper         | imental Results                                   | 127 |

|            | 6      | .4.1 I        | Equal Area Based PWM Technique (EAPWM)            | 127 |

|            | 6      | .4.2 I        | Frequency and Harmonic Estimation                 | 127 |

|            | 6      | .4.3 I        | Harmonic Reduction                                | 128 |

| 6.         | .5 F   | lutur         | e Research Issues                                 | 129 |

| Refere     | ences  | <b>S</b> .    |                                                   | 131 |

| Apper      | ndix . | <b>A:</b>     | DSP Programs                                      | A1  |

| A          | .1 A   | Activ         | e Power Filter                                    | A1  |

|            | A      | 1.1.1         | Main Module                                       | A1  |

|            | A      | 1.2           | Hysteresis PWM Module                             | A3  |

|            | A      | x.1.3         | Frequency Estimation Module                       | A3  |

|            | A      | 1.4           | Power Factor Calculation                          | A4  |

|            | A      | x.1.5         | Harmonic Magnitude and Phase Calculations         | A4  |

|            | A      | .1.6          | Filter Bank Parameterisation                      | A5  |

|            | A      | .1.7          | Checking the Harmonic Standard Recommended Values | A5  |

|            | A      | 1.8           | Initilasation                                     | A5  |

|            | A      | .1.9          | Harmonic Estimation Module                        | A6  |

|             | A.1.10 Reference Waveform Generation Module | A7   |

|-------------|---------------------------------------------|------|

| A.2         | Equal Area PWM Technique                    | A7   |

|             | A.2.1 Look up Table                         | A8   |

|             | A.2.2 Switching Sequences                   | AS   |

|             | A.2.3 Sign Function                         | A9   |

| Appendix    | B: Micro Controller Programs                | B1   |

| <b>B.</b> 1 | Filter Bank                                 | B1   |

| <b>B.2</b>  | Hysteresis PWM                              | B3   |

| Annendiv    | C · Recommendations of Harmonic Standards   | . C1 |

# **LIST OF FIGURES**

| Figure 1.1:  | Harmonic reduction techniques [17].                                                                                                                                                                          | 5  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2:  | Passive power filter                                                                                                                                                                                         | 6  |

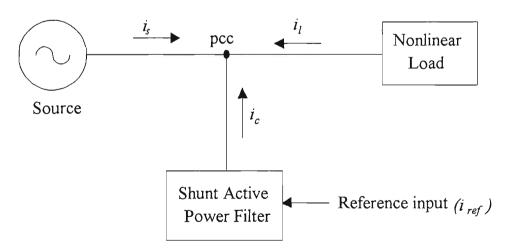

| Figure 1.3:  | Basic principle of shunt active power filter.                                                                                                                                                                | 7  |

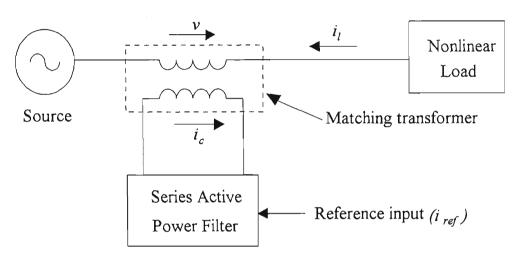

| Figure 1.4:  | Basic principle of series active power filter.                                                                                                                                                               | 8  |

| Figure 2.1:  | Natural PWM technique                                                                                                                                                                                        | 16 |

| Figure 2.2:  | Unipolar natural sampling PWM patterns.                                                                                                                                                                      | 17 |

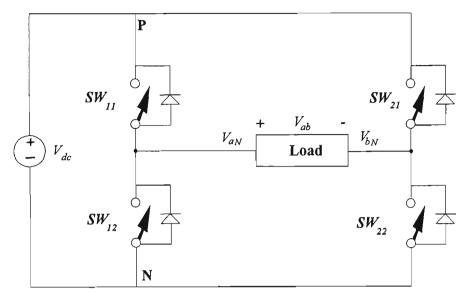

| Figure 2.3:  | Full-bridge inverter                                                                                                                                                                                         | 18 |

| Figure 2.4:  | Regular sampling PWM technique                                                                                                                                                                               | 18 |

| Figure 2.5:  | Unipolar regular asymmetric sampling PWM pattern.                                                                                                                                                            | 19 |

| Figure 2.6:  | Equal sampling technique                                                                                                                                                                                     | 20 |

| Figure 2.7:  | Centroid based PWM technique [40].                                                                                                                                                                           | 21 |

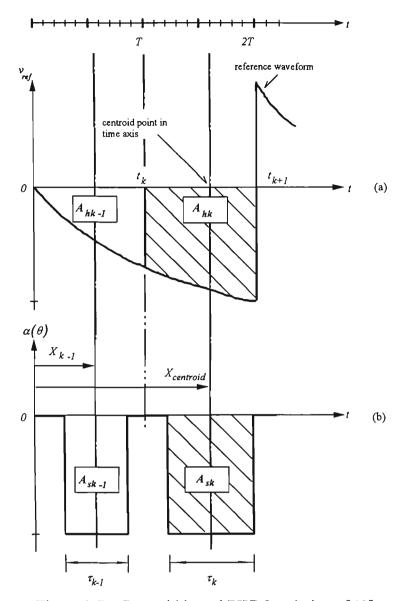

| Figure 2.8:  | Equal area based PWM technique.                                                                                                                                                                              | 23 |

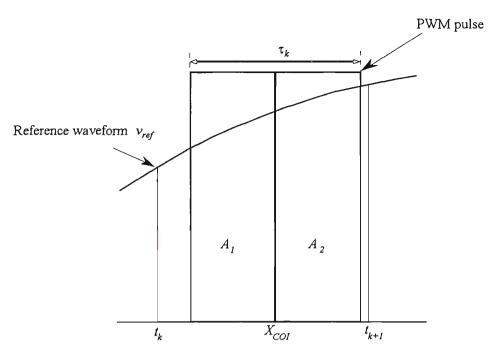

| Figure 2.9:  | Pulse positions for CBT PWM patterns.                                                                                                                                                                        | 25 |

| Figure 2.10: | Comparison between the pulse positions of the CBT and EAPWM techniques.                                                                                                                                      | 26 |

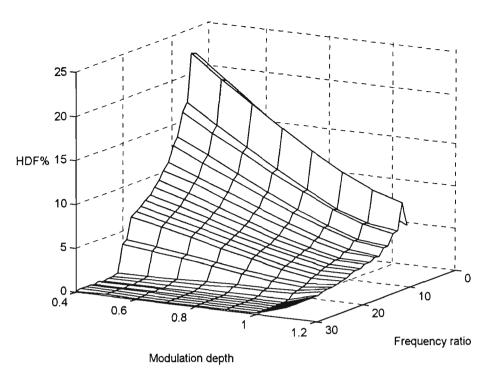

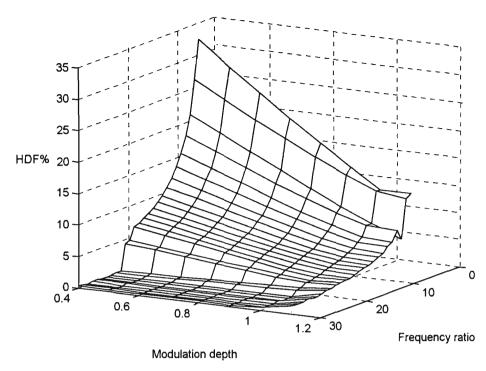

| Figure 2.11: | Harmonic distortion in CBT PWM technique.                                                                                                                                                                    | 28 |

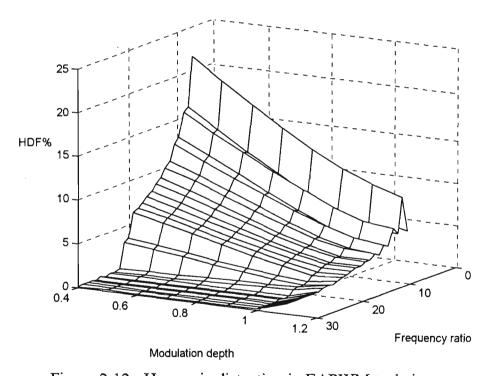

| Figure 2.12: | Harmonic distortion in EAPWM technique                                                                                                                                                                       | 28 |

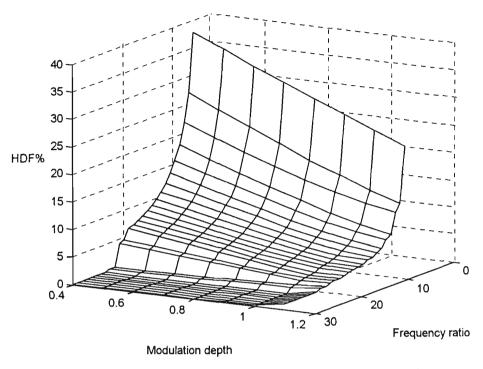

| Figure 2.13: | Harmonic distortion in EST PWM technique.                                                                                                                                                                    | 29 |

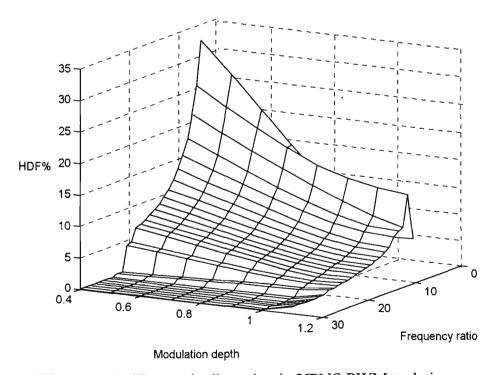

| Figure 2.14: | Harmonic distortion in UPNS PWM technique.                                                                                                                                                                   | 29 |

| Figure 2.15: | Harmonic distortion in UPRAS PWM technique                                                                                                                                                                   | 30 |

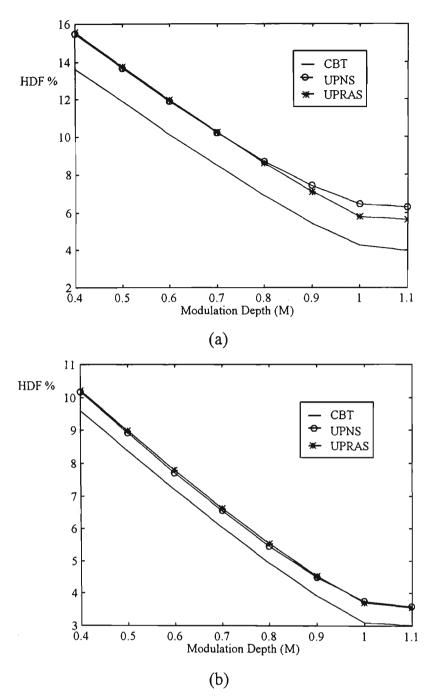

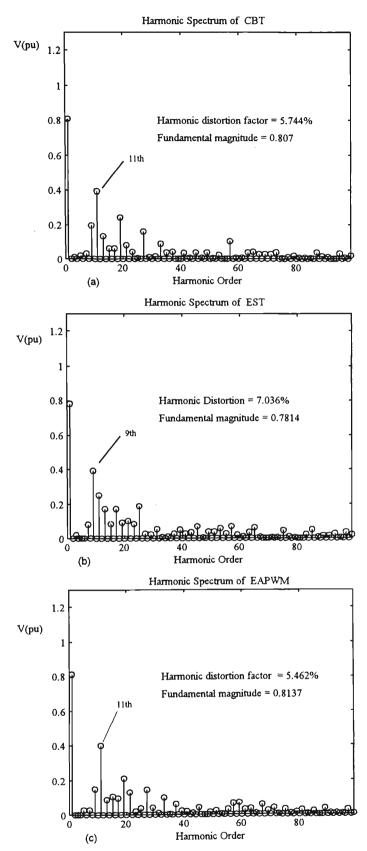

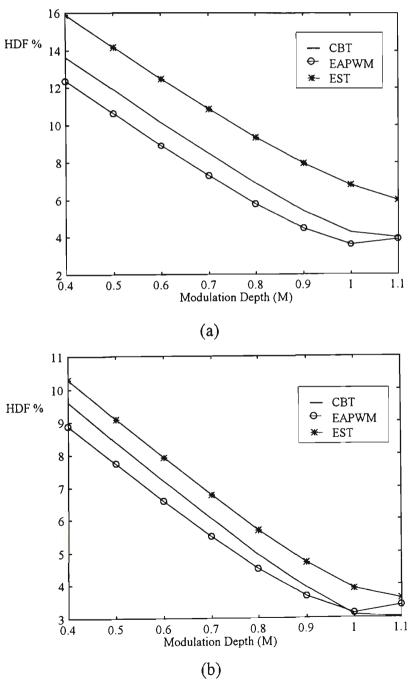

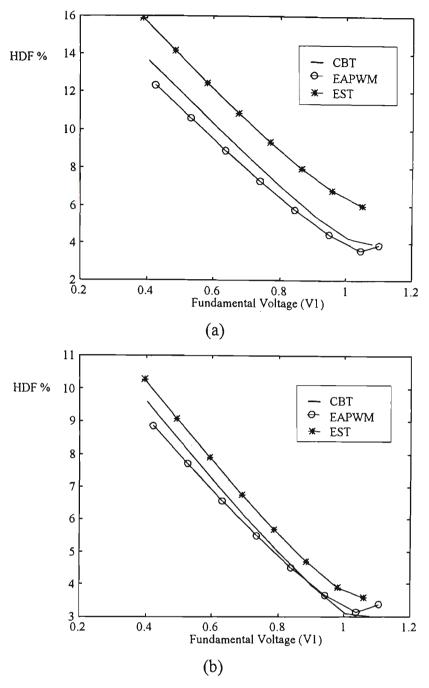

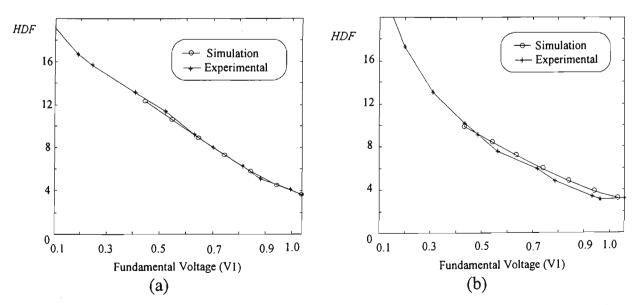

| Figure 2.16: | HDF vs. modulation depth for: (a) p=8, (b) p= 12.                                                                                                                                                            | 31 |

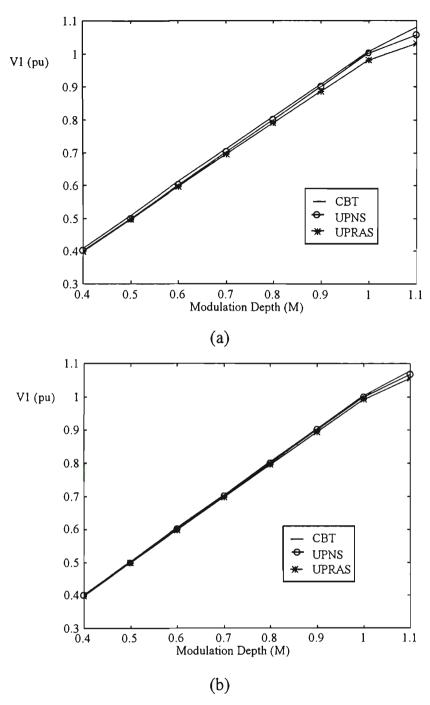

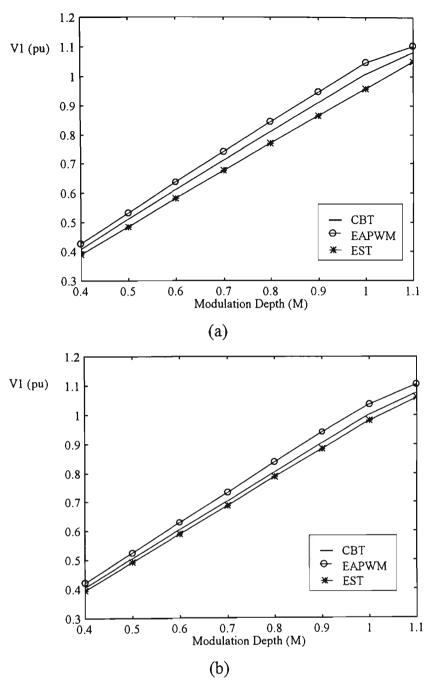

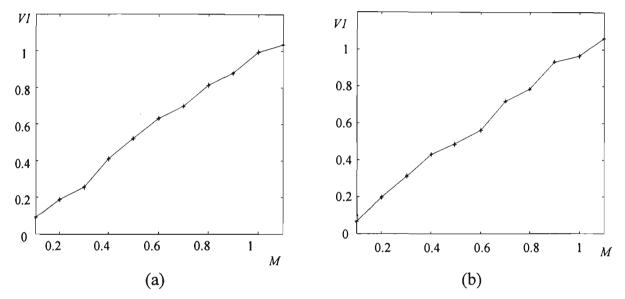

| Figure 2.17: | Fundamental voltage vs. modulation depth for: (a) $p=8$ , (b) $p=12$                                                                                                                                         | 32 |

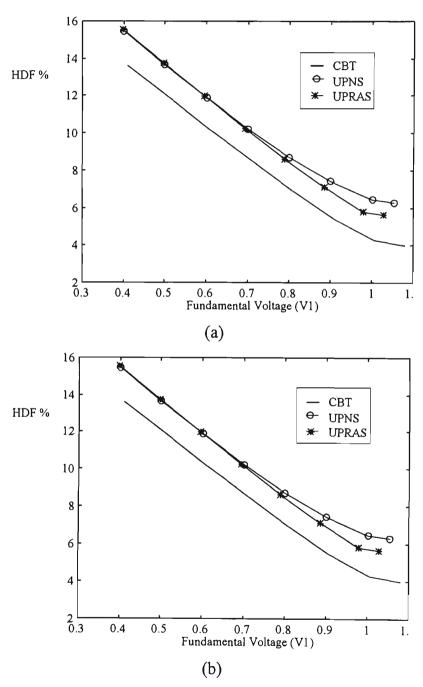

| Figure 2.18: | HDF vs fundamental voltage for: (a) $p=8$ , (b) $p=12$                                                                                                                                                       | 33 |

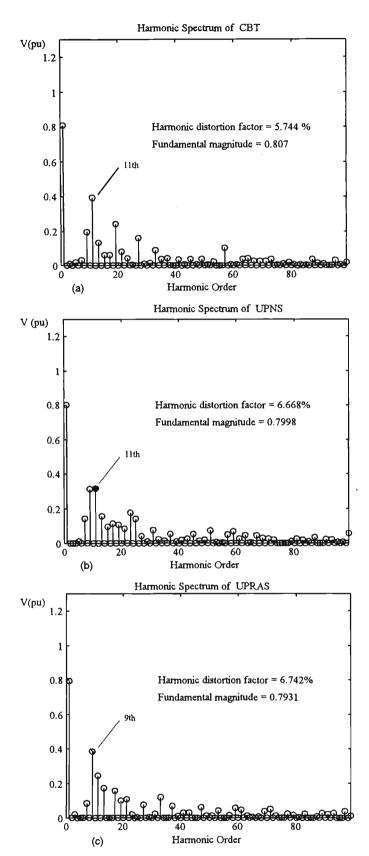

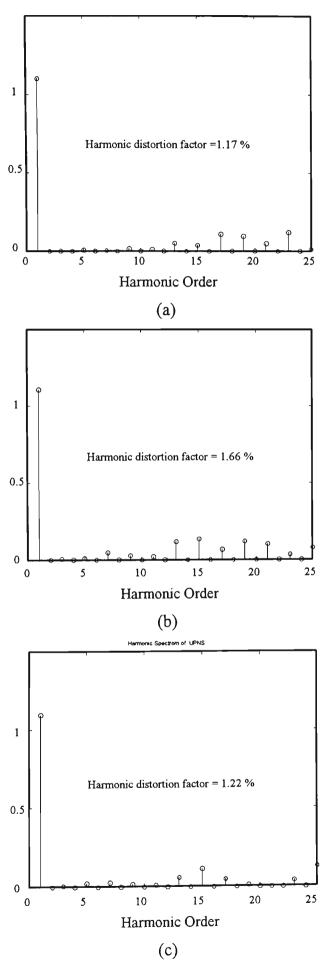

| Figure 2.19: | Harmonic spectrum: switching frequency ratio 10, modulation depth 0.8: (a) Centroid based technique(CBT), (b) Unipolar natural sampling technique (UPNS), (c) Regular asymmetric sampling technique (UPRAS). | 34 |

| Figure 2.20: | Harmonic spectrum: switching frequency ratio 10, modulation depth 0.8:  (a) Centroid based technique (CBT),  (b) Equal sampling technique (EST),  (c) Equal area based PWM technique (EAPWM) |    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.21: | HDF vs. modulation depth for: (a) $p=8$ , (b) $p=12$ .                                                                                                                                       | 37 |

| Figure 2.22: | Fundamental voltage vs. modulation depth for: (a) $p=8$ , (b) $p=12$                                                                                                                         | 38 |

| Figure 2.23: | HDF vs fundamental voltage for : (a) $p=8$ , (b) $p=12$                                                                                                                                      | 39 |

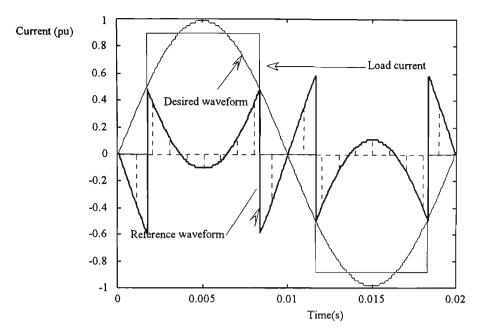

| Figure 2.24: | Current waveforms for predetermined harmonic cancellation                                                                                                                                    | 40 |

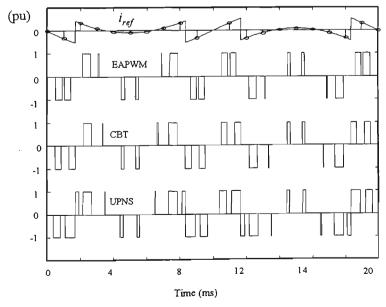

| Figure 2.25: | PWM pattern generated using: EAPWM, CBT and UPNS techniques                                                                                                                                  | 40 |

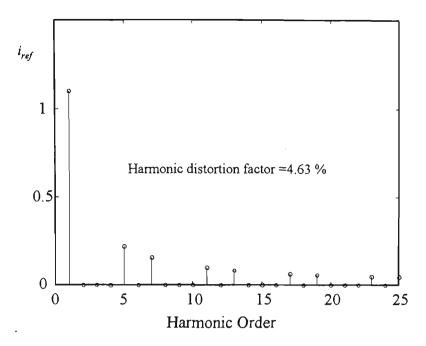

| Figure 2.26: | Harmonic spectrum of the load current waveform.                                                                                                                                              | 4] |

| Figure 2.27: | Frequency spectrum of the source current after compensation:  (a)EAPWM, (b) CBT and (c) UPNS                                                                                                 | 42 |

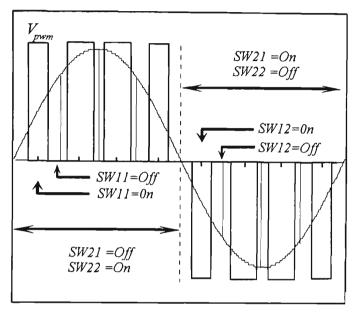

| Figure 2.28: | Proposed switching sequence.                                                                                                                                                                 | 44 |

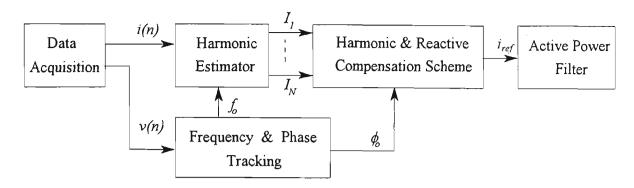

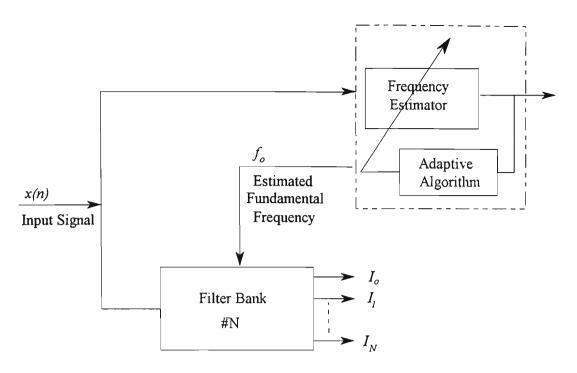

| Figure 3.1:  | Proposed harmonic estimation technique for active power filtering                                                                                                                            | 46 |

| Figure 3.2:  | Short term Fourier transform                                                                                                                                                                 | 49 |

| Figure 3.3:  | Filter bank based sliding measurement of power system harmonics                                                                                                                              | 50 |

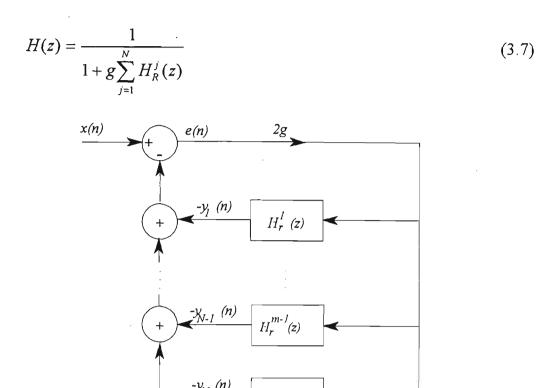

| Figure 3.4:  | Resonator based filter bank.                                                                                                                                                                 | 51 |

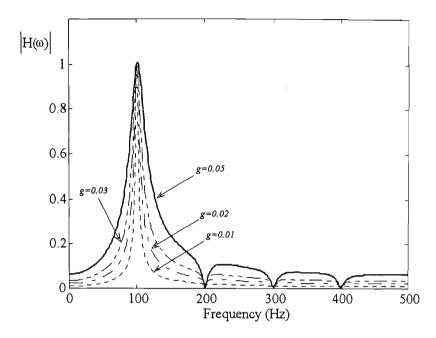

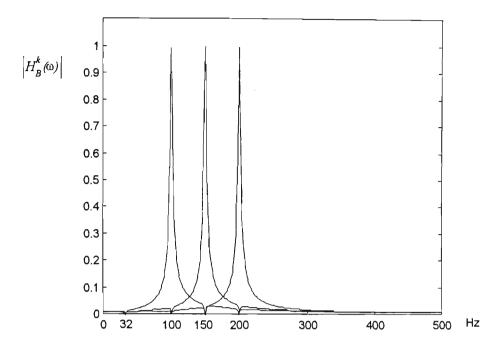

| Figure 3.5:  | Transfer function magnitudes of the filter bank for: $fI=100$ Hz and $g=0.01$ , $g=0.02$ , $g=0.03$ , $g=0.05$                                                                               | 52 |

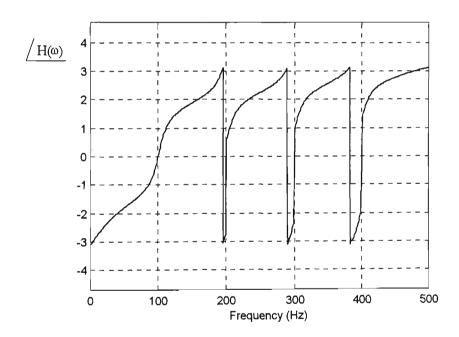

| Figure 3.6:  | The phase transfer functions of the filter bank for $fI=100$ Hz and, $g=0.05$ .                                                                                                              | 52 |

| Figure 3.7:  | The magnitude transfer functions the filter bank for $N = 4$ and $g = 0.01$ : $f1=32$ Hz, $f2=100$ Hz, $f3=150$ Hz, $f4=200$ Hz [72]                                                         | 53 |

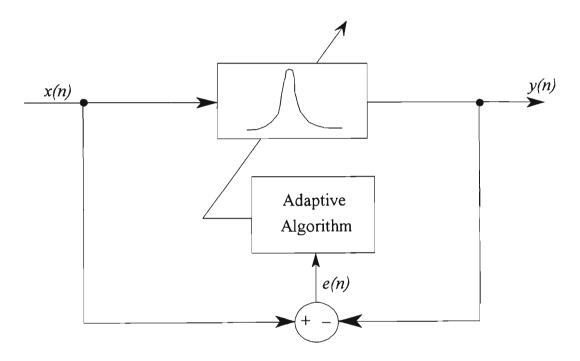

| Figure 3.8:  | Adaptive IIR filtering                                                                                                                                                                       | 56 |

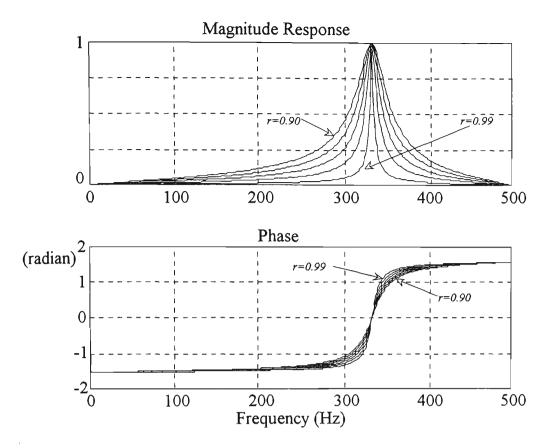

| Figure 3.9:  | Frequency response of IIR filter for: $fp=320$ Hz and $r=0.9-0.99$                                                                                                                           | 57 |

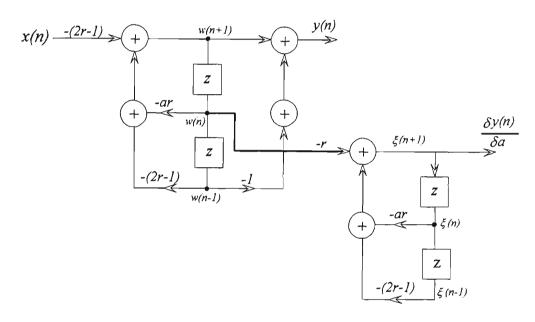

| Figure 3.10: | The flow-graph of the filter implantation.                                                                                                                                                   | 58 |

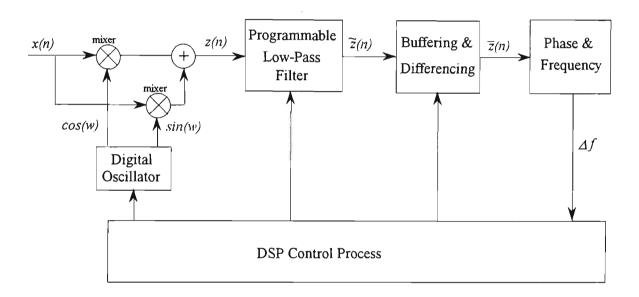

| Figure 3.11: | Digital FM demodulator frequency tracking                                                                                                                                                    | 59 |

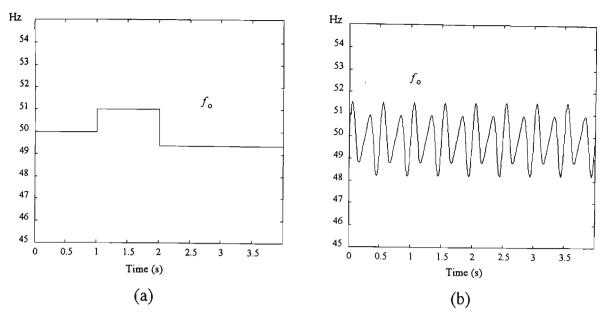

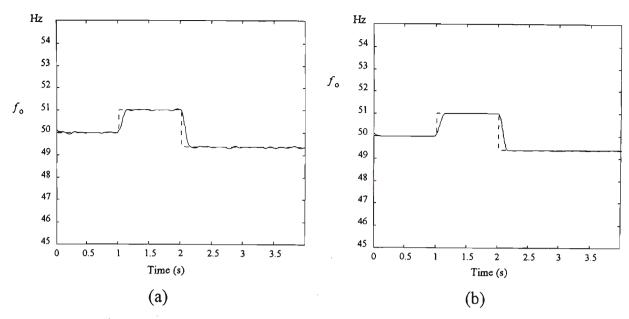

| Figure 3.12: | Fundamental frequency variation with time:(a) step changes, (b) sinusoidal changes.                                                                                                          | 62 |

| Figure 3.13: | Fundamental frequency tracking for step changes: (a) $\mu$ =0.01, $\Gamma$ =1, $\gamma$ =0.9, SNR= 25 dB, (b) $\mu$ =0.03, $\Gamma$ =1, $\gamma$ =0.9, SNR=40 dB                             | 62 |

| Figure 3.14: | Fundamental frequency tracking sinusoidal changes: (a) $\mu$ =0.01, $\Gamma$ =1, $\gamma$ =0.9, SNR= 25 dB, (b) $\mu$ =0.03, $\Gamma$ =1, $\gamma$ =0.9, SNR=40 dB                           | 63 |

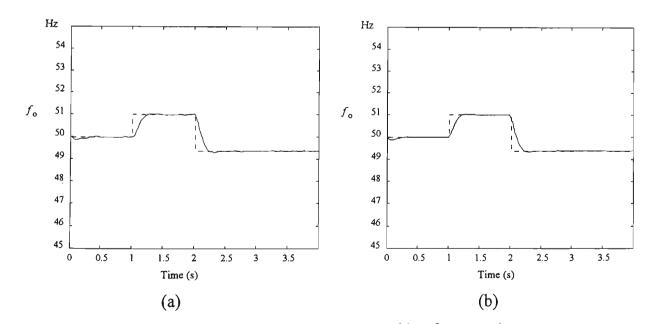

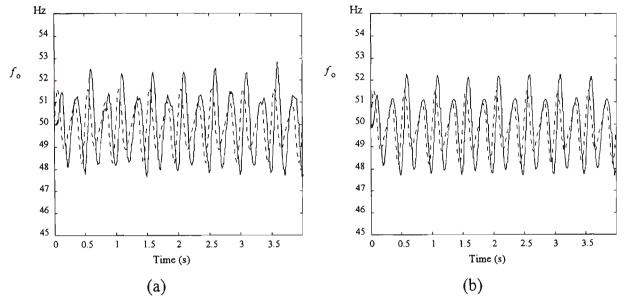

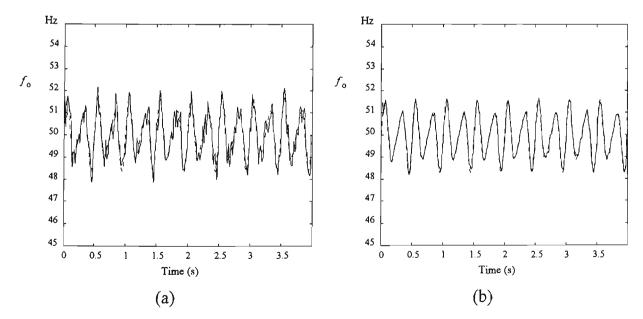

| Figure 3.15: | Fundamental frequency tracking for step changes: (a) fcut = 5 Hz,<br>NFIR=50, SNR=25 dB, (b) fcut = 5 Hz, NFIR=30, SNR=40 dB                                                                 | 64 |

| Figure 3,16: | Fundamental frequency tracking for sinusoidal changes: (a) fcut = 5 Hz, NFIR=50, SNR=25 dB, (b) fcut = 5 Hz, NFIR=30, SNR=40 dB                                                              |    |

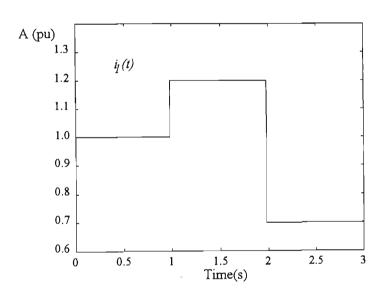

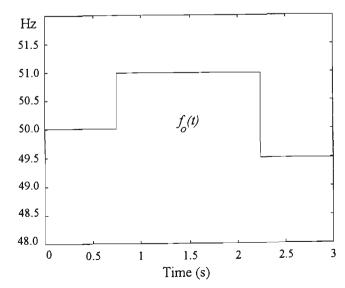

| Figure 3.17: | The magnitude variation of test load current signal.                                                                                                                                         |    |

| Figure 3.18: | The fundamental frequency variation of test load current signal.                                     | 65  |

|--------------|------------------------------------------------------------------------------------------------------|-----|

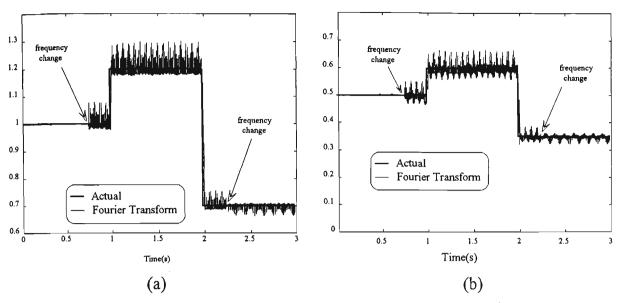

| Figure 3.19: | Actual and estimated amplitude: (a) Fundamental, (b) 3rd order harmonic                              | .67 |

| Figure 3.20: | Actual and estimated amplitude: (a) 5th, (b) 25th order harmonic                                     | 67  |

| Figure 3.21: | Actual and estimated amplitude: (a) 26th, (b) 29th order harmonic                                    | 68  |

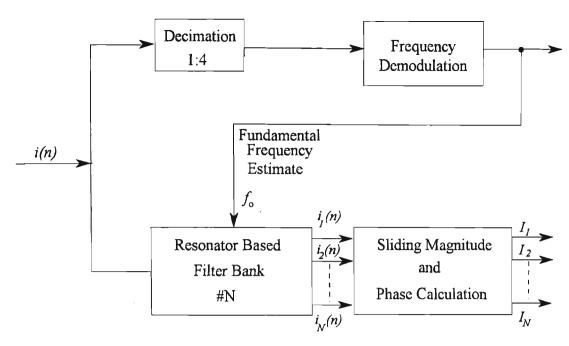

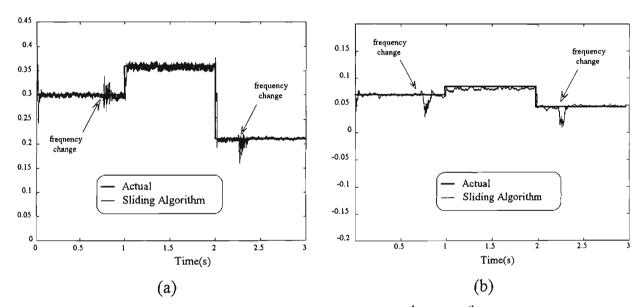

| Figure 3.22: | Proposed technique for sliding measurement of power system harmonics.                                | 69  |

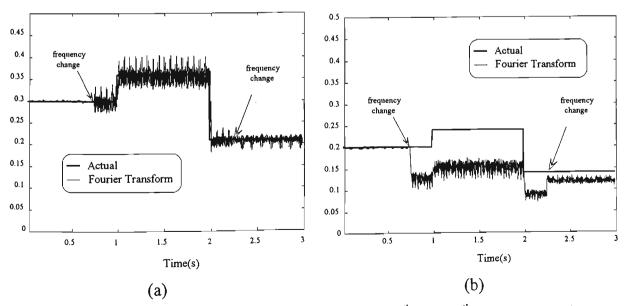

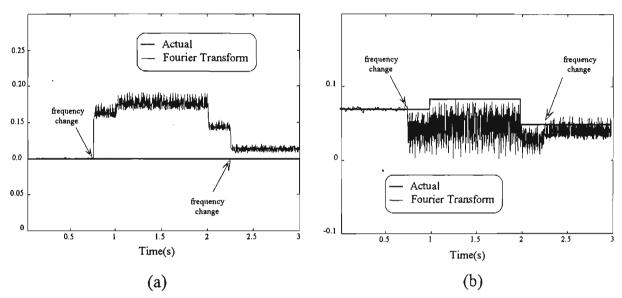

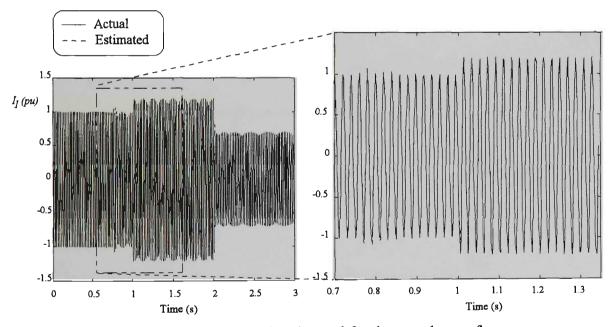

| Figure 3.23: | Actual and estimated fundamental waveforms                                                           | 69  |

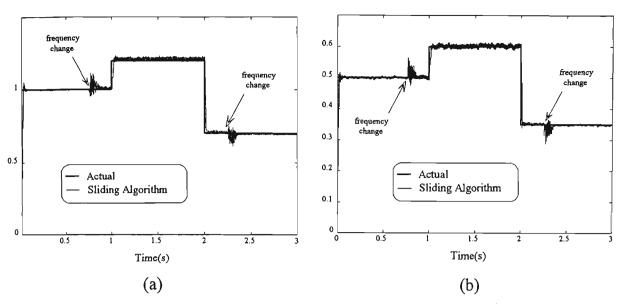

| Figure 3.24: | Actual and estimated amplitude: (a) Fundamental, (b) 3rd harmonic                                    | 70  |

| Figure 3.25: | Actual and estimated amplitude: (a) 5th, (b) 29th order harmonics                                    | 70  |

| Figure 4.1:  | Functional block diagram of the proposed active power filter.                                        | 74  |

| Figure 4.2:  | Flow chart of control strategy                                                                       | 76  |

| Figure 4.3:  | Digital FM demodulator                                                                               | 77  |

| Figure 4.4:  | Filter bank harmonic estimation and generation of APF reference wavefor                              |     |

| Figure 4.5:  | Hysteresis current control                                                                           | 85  |

| Figure 4.6:  | The circuit diagram of the proposed active power filter.                                             | 86  |

| Figure 4.7:  | The schematic diagram of the current sensing and conditioning circuitry                              | 87  |

| Figure 4.8:  | The schematic diagram of the voltage attenuation circuit                                             | 88  |

| Figure 4.9:  | Block diagram of ADC64 data acquisition system.                                                      | 89  |

| Figure 4.10: | The simulated hardware on SPECS.                                                                     | 90  |

| Figure 4.11: | The steady state performance of active power filter.                                                 | 91  |

| Figure 4.12: | DC link voltage frequency spectrum.                                                                  | 92  |

| Figure 4.13: | Load current frequency spectrum.                                                                     | 92  |

| Figure 4.14: | AC supply source current frequency spectrum after compensation                                       | 93  |

| Figure 4.15: | Active power filter current frequency spectrum.                                                      | 93  |

| Figure 4.16: | Transient performance of active power filter after a load change                                     | 94  |

| Figure 5.1:  | The schematic of the EAPWM test configuration.                                                       | 98  |

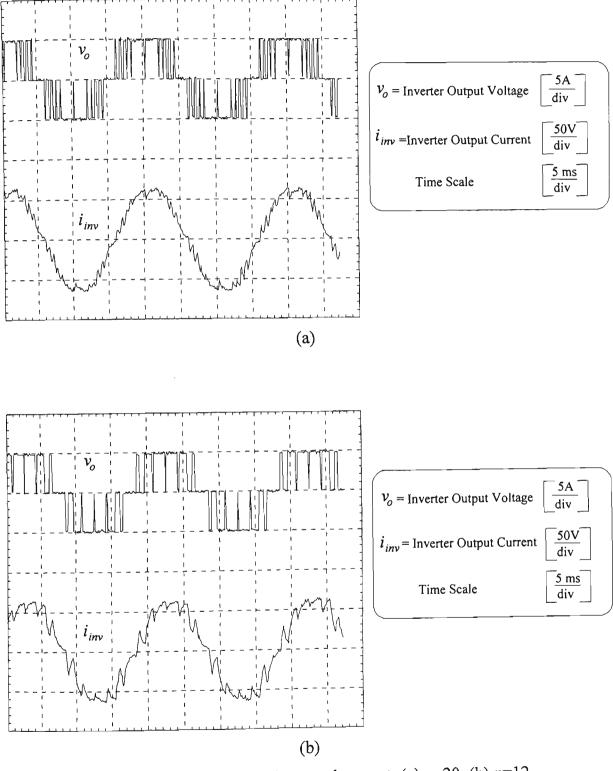

| Figure 5.2:  | The inverter voltage and current: (a) $p=20$ , (b) $p=12$                                            | 99  |

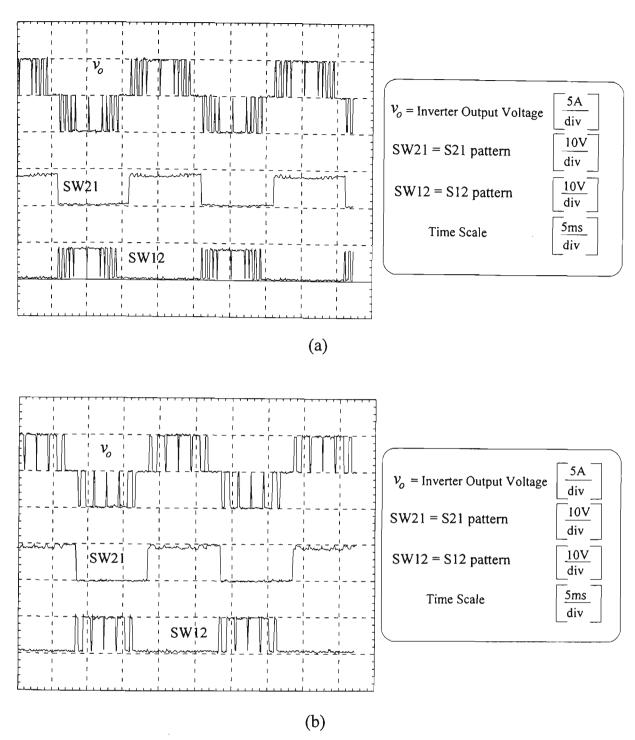

| Figure 5.3:  | The inverter voltage and switching patterns for $SW_{21}$ and $SW_{12}$ :  (a) $p=20$ , (b) $p=12$ . |     |

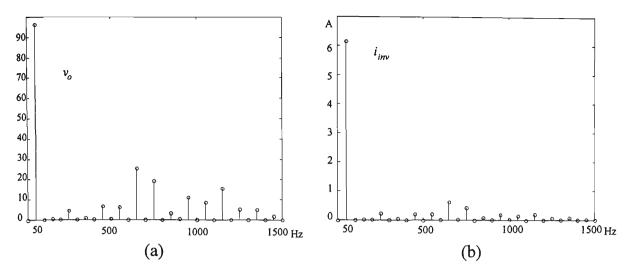

| Figure 5.4:  | Frequency spectrum of: (a) the inverter output voltage, (b) load current ( $p=12, M=1.0$ ).          | 01  |

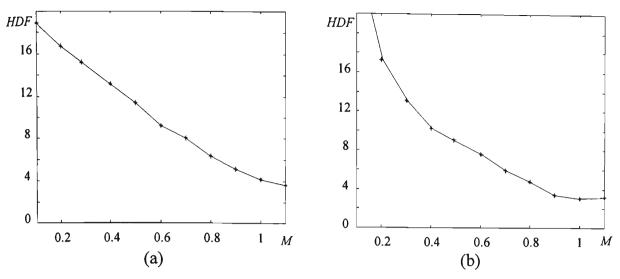

| Figure 5.5:  | HDF versus modulation depth for frequency ratios: (a) $p=8$ ,(b) $p=121$                             | 02  |

| Figure 5.6:  | Per Unit fundamental voltage $(V_I)$ versus modulation depth $(M)$ for: (a) $p=8$ , (b) $p=12$ .     | 02  |

| Figure 5.7:  | HDF versus fundamental voltage for frequency ratios: (a) $p=8$ ,(b) $p=12.1$                         | 02  |

| Figure 5.8:  | The estimated frequency and the voltage waveform.                                                                                                                           | 103 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.9:  | The estimated fundamental current $(I_I)$ , $3^{rd}$ harmonic $(I_3)$ , in relation to supply voltage $(V_s)$ and load current $(I_{load})$ .                               | 105 |

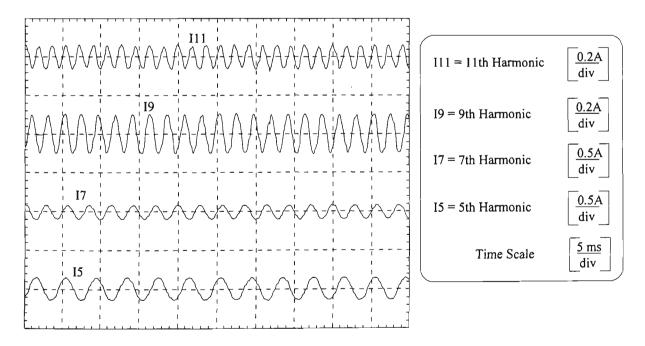

| Figure 5.10: | The estimated current harmonic waveforms: 11 <sup>th</sup> , 9 <sup>th</sup> , 7 <sup>th</sup> and 5 <sup>th</sup>                                                          | 105 |

| Figure 5.11: | The estimated current harmonic waveforms: 19 <sup>th</sup> , 17 <sup>th</sup> , 15 <sup>th</sup> and 13 <sup>th</sup>                                                       | 106 |

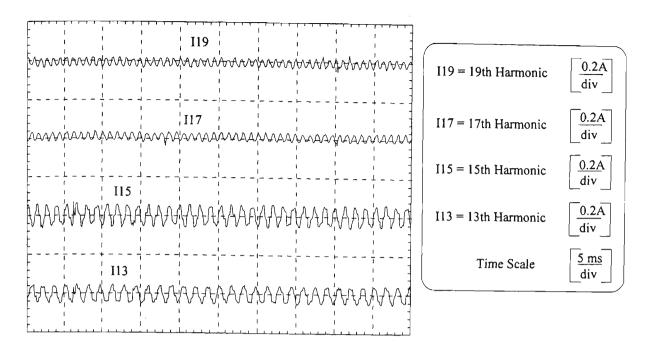

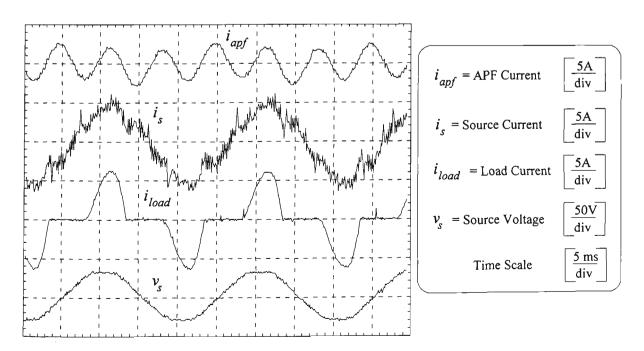

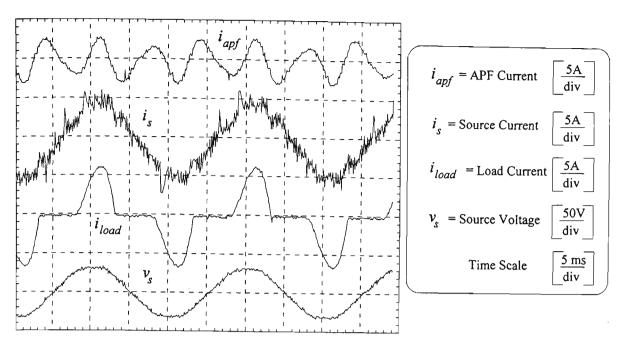

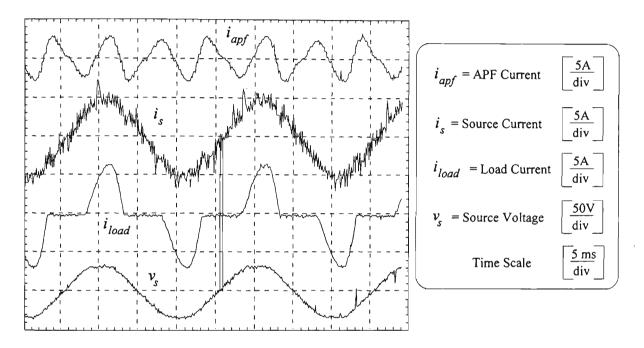

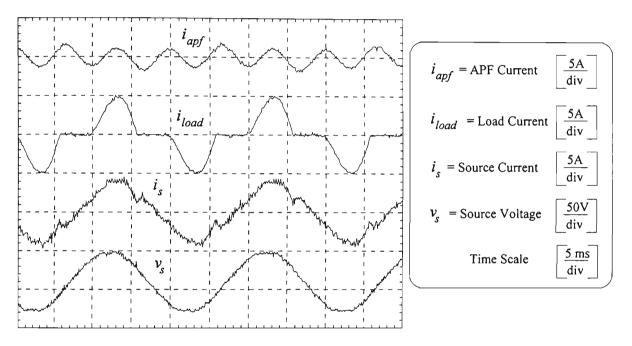

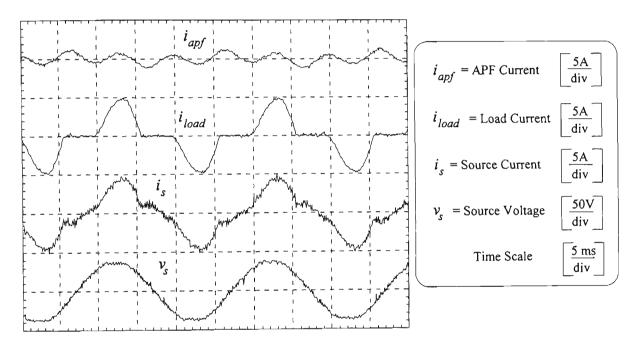

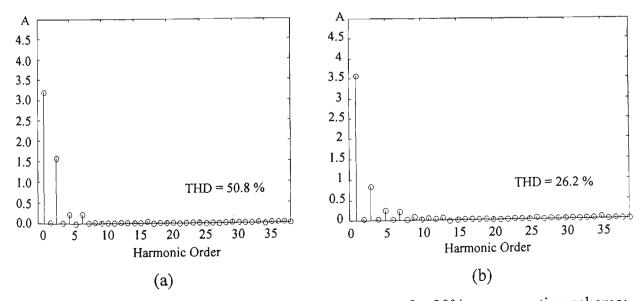

| Figure 5.12: | Full harmonic compensation scheme                                                                                                                                           | 107 |

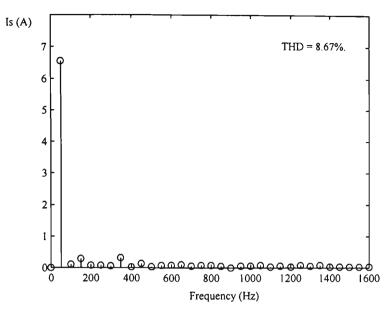

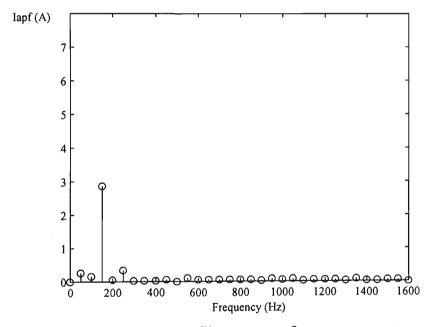

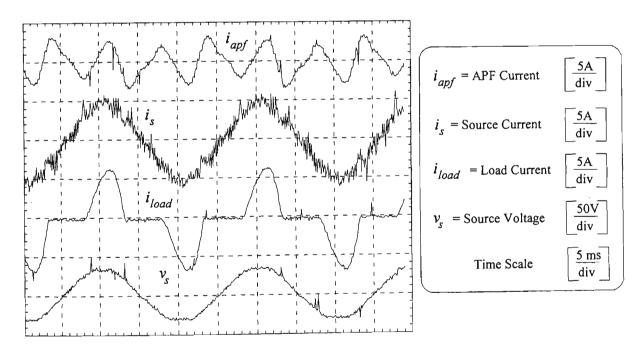

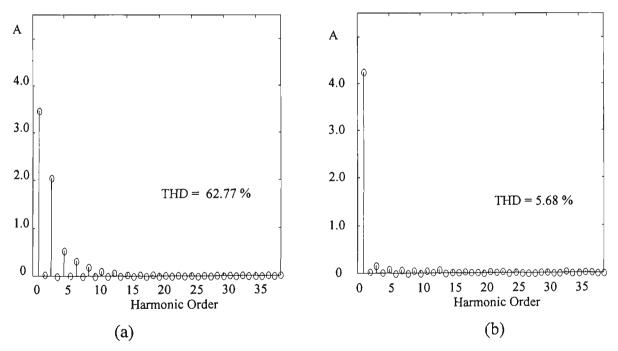

| Figure 5.13: | The frequency spectrum of source current; (a) before and (b) after compensation.                                                                                            | 108 |

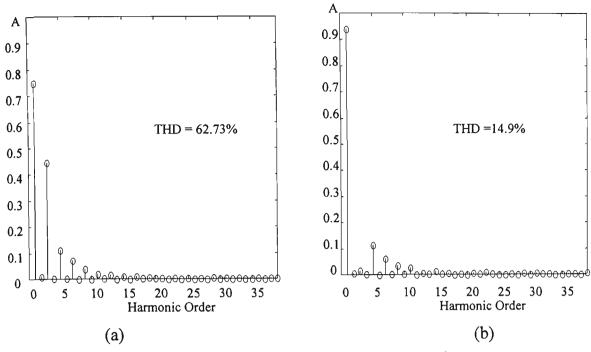

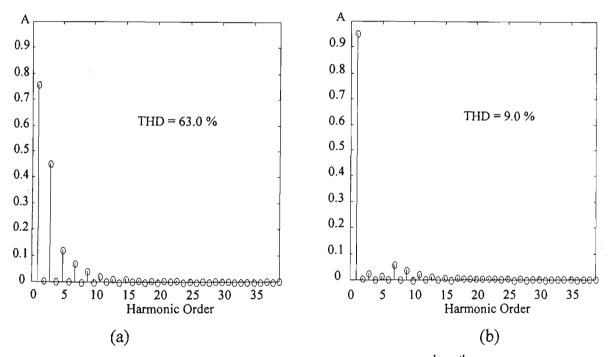

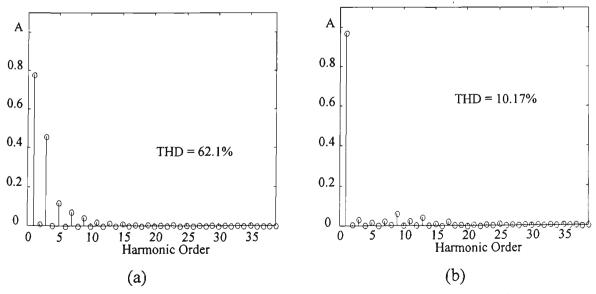

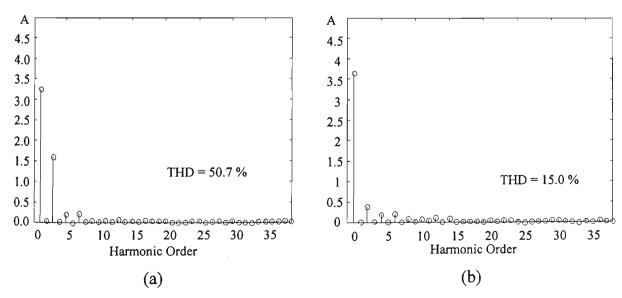

| Figure 5.14: | Selective harmonic compensation; 3 <sup>rd</sup> harmonic                                                                                                                   | 109 |

| Figure 5.15: | The frequency spectrum of source current for 3 <sup>rd</sup> harmonic reduction (a) before and (b) after compensation.                                                      | 110 |

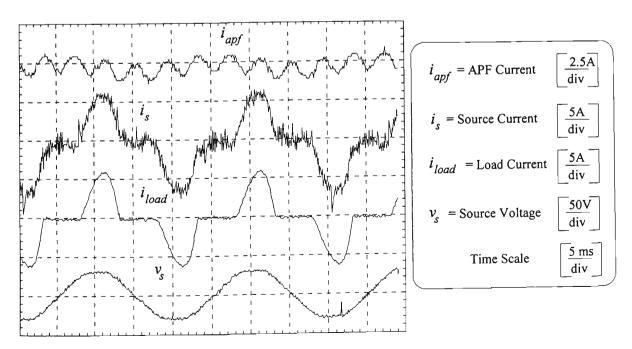

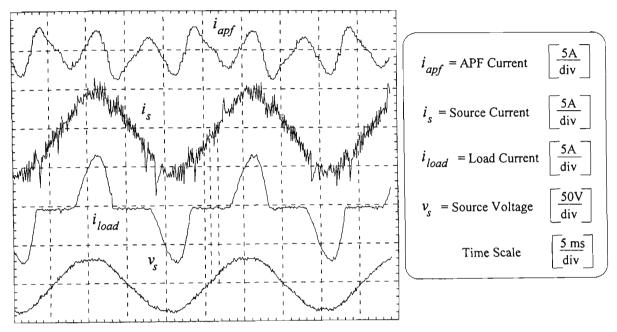

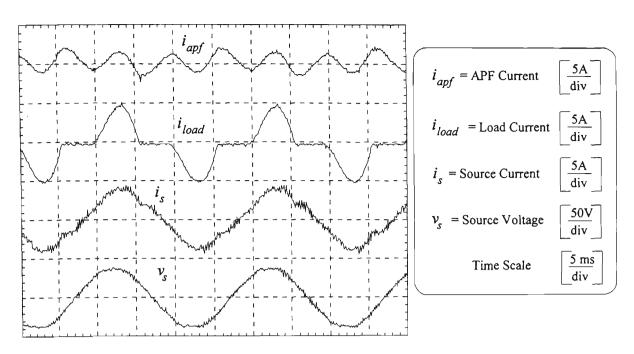

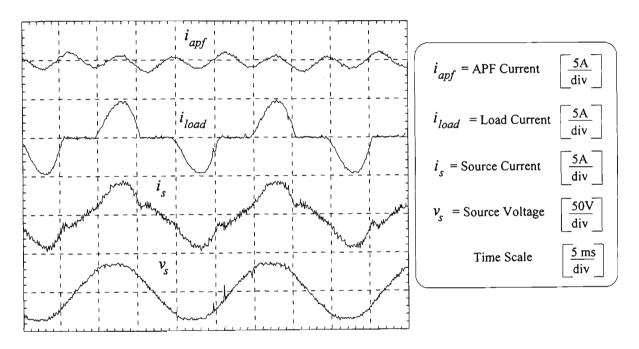

| Figure 5.16: | Selective harmonic compensation; 5 <sup>th</sup> harmonic                                                                                                                   | 110 |

| Figure 5.17: | The frequency spectrum of source current for 5 <sup>th</sup> harmonic reduction (a) before and (b) after compensation.                                                      | 111 |

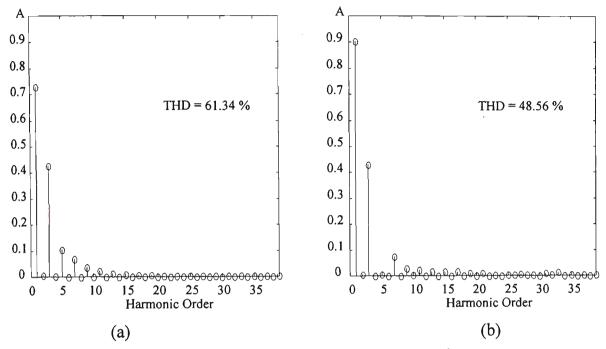

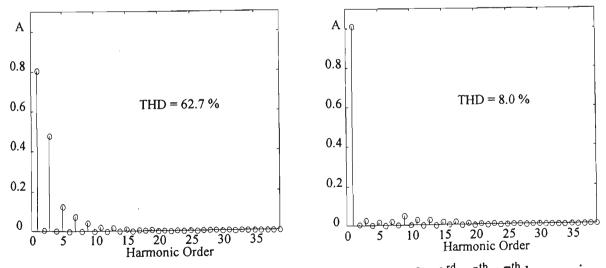

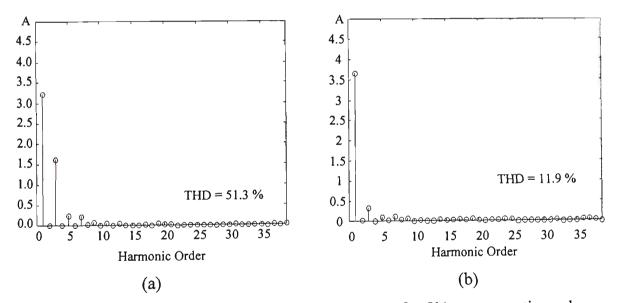

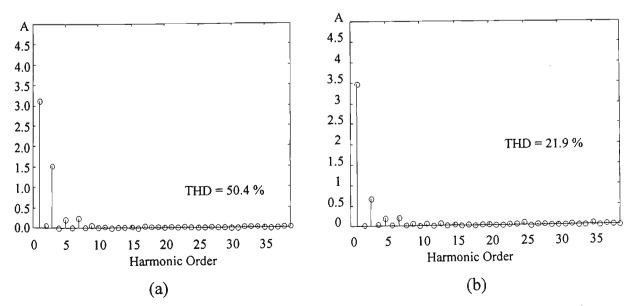

| Figure 5.18: | Selective harmonic compensation; $3^{rd} + 5^{th}$ harmonics                                                                                                                |     |

| Figure 5.19: | The frequency spectrum of source current for 3 <sup>rd</sup> +5 <sup>th</sup> harmonic reduction (a) before and (b) after compensation                                      | 112 |

| Figure 5.20: | Selective harmonic compensation; 3 <sup>rd</sup> +5 <sup>th</sup> +7 <sup>th</sup> harmonics                                                                                | 113 |

| Figure 5.21: | The frequency spectrum of source current for 3 <sup>rd</sup> +5 <sup>th</sup> +7 <sup>th</sup> harmonic reduction (a) before and (b) after compensation.                    | 113 |

| Figure 5.22: | Selective harmonic compensation; $3^{rd} + 5^{th} + 7^{th}$ harmonics and reactive power compensation.                                                                      | 114 |

| Figure 5.23: | The frequency spectrum of source current for 3 <sup>rd</sup> +5 <sup>th</sup> +7 <sup>th</sup> harmonic reduction (a) before and (b) after compensation with reactive power | 114 |

| Figure 5.24: | The 5% harmonic compensation scheme                                                                                                                                         | 116 |

| Figure 5.25: | The frequency spectrum of source current for 5% compensation scheme: (a) before and (b) after compensation                                                                  | 116 |

| Figure 5.26: | The 10% harmonic compensation scheme.                                                                                                                                       | 117 |

| Figure 5.27: | The frequency spectrum of source current for 10% compensation scheme: (a) before and (b) after compensation                                                                 | 117 |

| Figure 5.28: | The 15% harmonic compensation scheme.                                                                                                                                       | 118 |

| Figure 5.29: | The frequency spectrum of source current for 15% compensation scheme: (a) before and (b) after compensation                                                                 | 118 |

| Figure 5.30: | The 20% harmonic compensation scheme.                                                                                                                                       | 119 |

| •            | The frequency spectrum of source current for 20% compensation scheme: (a) before and (b) after compensation                                                                 |     |

| Figure 5.32: | Transient Performance of APF with harmonic standard (5%)                                                                                                                    | 121 |

| Figure 5.33: | Transient Performance of APF with harmonic standard (5%)                                                                                                                    | 121 |

# LIST OF TABLES

| Table 2.1: | The switching combinations                                    | 43  |

|------------|---------------------------------------------------------------|-----|

| Table 3.1: | Computational burden in terms of FLOPS.                       | 71  |

| Table 4.1: | The simulated system parameters                               | 90  |

| Table 5.1: | Load and inverter filter data.                                | 97  |

| Table 5.2: | Computational burden of proposed control strategy             | 106 |

| Table 5.3: | The comparison of the selected schemes for harmonic reduction | 120 |

## LIST OF SYMBOLS

$V_a$  Partial derivative of the mean squared error

$\gamma$  Forgetting factor

$\Gamma$  Smoothed estimate of the power of the  $\nabla_a$

$\omega$  Angular phase

$\Phi$  Phase angle

$\varepsilon$  Small positive real number

$\mu$  Step size

$\xi$  Variance of the error signal

$\varepsilon(n)$  White noise

$\Delta f$  Fundamental frequency deviation

$\Delta I_{high}$  Upper boundary of the hysteresis band

$\Delta I_{low}$  Lower boundary of the hysteresis band

$\tau_k$   $k^{th}$  pulsewidth

$\phi_h$  Magnitude of the  $h^{th}$  input signal

a Bandpass filter parameter

$A_h$  Magnitude of the  $h^{th}$  input signal

$C_{dc}$  DC link capacitor

$C_k$  Fourier coefficients of the output signal

$D_k$  Fourier coefficients of the output signal

$E(e^2)$  Expected error

e(n) Error signal

f<sub>o</sub> Reference waveform frequency

$f_p$  Centre frequency

$f_s$  Sampling frequency

$f_{sw}$  Switching frequency

g Filter bank feedback gain

h Harmonic order

$H_{BP}(z)$ Bandpass transfer function  $H_r(z)$ Resonator transfer function

Inverter compensation current  $i_{comp}$

$i_{load}$ Load current

$i_{apf}$

Compensating switching losses current ilosses

Active filter current

Harmonic amplitude vector  $I_h$

$I_h^{ref}$ Reference load current weighting

$i_{reactive}$ Reactive current of the load

Active power filter reference current  $i_{ref}$

i, Source current

$K_{reactive}$ Constant which controls the level of fundamental reactive power

$L_{apf}$ Active power filter Inductance

MModulation Index

N Number of filter in filter bank

p Frequency ratio

$\overline{p}$ Average power

$\widetilde{p}$ Oscillatory power.

p(t)Instantaneous power

Bandpass IIR filter bandwidth parameter r

SWSwitching command

Triangular waveform period  $T_{tri}$

$V_{dc}$ DC voltage

Peak magnitude of reference waveform  $V_m$

$v_{ref}$ Reference waveform

$\nu_s$ Source voltage

$V_{tri}$ Triangular voltage waveform

W(n)Window function

x(t)Input signal

Centroid, pulse position  $X_{centroid}$

Centre of integration  $X_{COI}$  $y^f(n)$ Estimate for  $\frac{\partial y(n)}{\partial x}$

## **CHAPTER**

# 1.

## **PRELIMINARY**

#### 1.1 Introduction

The widespread use of power electronics-based loads to improve energy efficiency and flexibility has increased the harmonic distortion levels in end use facilities and on the overall power system. The need for reducing distortion in power systems has led to a great deal of research attention in the area of power quality [1].

Regulatory organisations have increased their efforts towards establishing standards which limit the harmonic pollution in power systems [2-5]. Harmonic standards recommend limits on harmonic distortion in two ways. First, limits are placed on the amount of the harmonic current that consumers can inject into a utility network as a preventative action and secondly limits are imposed on the levels of harmonic voltages that utilities can supply to consumers.

#### 1.2 POWER SYSTEM HARMONICS

As stated above, the proliferation of semiconductor devices used in many electronic systems that are essentially exhibiting nonlinear voltage-current characteristics lead to excessive power system voltage and current distortions. The distorted supply voltage can cause further harmonic current distortions in other linear loads [6, 7]. Most distorted current waveforms contain harmonic components which are primarily integer multiples of

the fundamental frequency. However, it is also possible to have non-integer multiples for certain types of loads.

#### 1.2.1 Harmonic Sources

There are many types of nonlinear loads that cause current harmonics. The largest types of nonlinear loads are power electronic converters. These include high voltage DC (HVDC) stations, AC and DC variable speed drives and diode rectifiers systems that are found in many electrical appliances such as televisions and computers. Other nonlinear sources of harmonics include arc furnaces, transformer magnetising impedances, switched mode power supplies and fluorescent lights.

#### 1.2.2 Effects of Harmonic

The harmonic currents that are injected into a power system by harmonic sources can affect the power system voltage and subsequently customer equipment. On the power system side, harmonic currents are one of the main sources of disturbances, causing equipment overheating and deterioration of the performance of electronic equipment. The impact is worse when network resonances amplify harmonic currents. Harmonics may also interfere with relaying and metering to some degree [8]. They can cause interferences with power system control including ripple control, remote load control, protection systems and power plant excitation systems [9]. Harmonics can also cause thyristor firing errors in converter and static var compensator (SVC) installations, metering inaccuracies and false tripping of protective devices.

On the consumer side, the performance of equipment such as motor drives and computer power supplies can be adversely affected by harmonics. The higher order harmonics cause interferences on communication lines or electronically controlled equipment while lower order harmonics increase the heat losses in equipment. Some of these heating problems are proportional to frequency and some are proportional to the square of the frequency which can ultimately shorten the life-expectancy of equipment [8, 10-12].

#### 1.2.3 Measurement of Harmonics

Accurate measurement of power system voltage and current harmonics is necessary to analyse and predict the harmonic behaviour of a power system. The harmonic quantities of interest include the magnitude, phase, and their variation with respect to time.

#### 1.2.3.1 Measurement Techniques

Harmonic measurement techniques are classified into off-line and on-line techniques. Off-line techniques are usually used to identify the harmonics in a stationary signal whereas on-line techniques are used to track the dynamic variation of non-stationary harmonic signals. The non-stationary signals, such as power system voltage and current waveforms are characterised by the changing features in their frequency content and magnitude with respect to time. Therefore, on-line measurement of fundamental frequency and harmonics of such signals require sliding measurement techniques such as digital filtering and short-term Fourier transform. A detailed description of these methods will be presented in Chapter 3.

#### 1.2.4 Standards on Harmonics

Harmonic standards provide guidelines, recommendations, and limits to help assure compatibility between end use equipment and the power system. They also give utilities and customers information about the environment in which equipment is expected to work.

The primary objective of a harmonic standards is to limit actual harmonic voltages on supply systems to acceptable levels (compatibility levels) that will not result in adverse effects on sensitive equipment. Since the harmonic voltages result from harmonic currents and power system impedances, harmonic standards provide guidance on the limitation of harmonic currents injected into power system [13]. Some of these standards also provide information that can be used for economic evaluation of harmonic reduction techniques [10, 14].

#### 1.2.4.1 Australian Standards on Harmonics

The Australian Standard, AS2279.2-91 [4] recommends that the maximum level for total voltage harmonic distortion in industrial applications should be 5%. Further, the above standard applies limits of 2% and 4% for individual even and odd harmonics respectively. The limits may be increased at the discretion of the utilities, if substantiated by a thorough engineering assessment [4]. The utilities can further reduce these levels based on individual agreements [15].

#### 1.3 COMPENSATION OF HARMONICS

When a harmonic source is identified and classified, it is then the responsibility of either the consumer or the utility or both parties to reduce the resulting harmonic distortion level on the power system. When harmonic levels exceed the compatibility limits of power system equipment, appropriate solutions should be employed for mitigation of harmonic effects on equipment. These solutions consist of a reduction of harmonic levels on power system voltage and current or an increase in the levels of compatibility of equipment against the harmonic distortion.

The harmonic compensation will be an extremely cost-sensitive issue when utilities start to enforce harmonic standards. Therefore, the task of choosing a reliable and economical methodology for harmonic reduction from both the industrial end user and utility perspective becomes very important [16]. In the next section a brief review of common harmonic reduction techniques is presented.

### 1.3.1 Harmonic Reduction Techniques

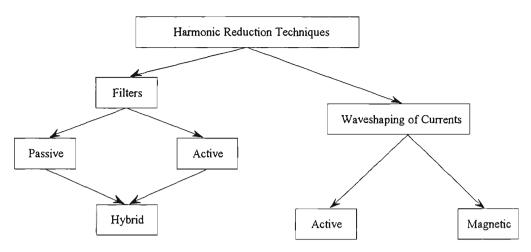

Harmonic reduction techniques can be classified into two categories including; wave-shaping and filtering techniques as shown in Figure 1.1 [16-18]. These techniques have been chosen by their ability to comply with the harmonic standards, particularly the IEEE-519 [3] requirement on total harmonic distortion (THD) level of connected loads. However, any comparison on the effectiveness of these techniques depends on the type and operating conditions of the load [17].

Figure 1.1: Harmonic reduction techniques [17].

In magnetic wave-shaping techniques, the line currents are shaped to have a sinusoidal waveform using magnetic devices such as differential delta transformers or a combination of semiconductor devices together with transformers [19]. Active wave-shaping techniques require controlling the semiconductor devices, such as power factor correction circuits or pulsewidth modulation (PWM) based rectifiers, to ensure that the line currents are sinusoidal [17].

External filters not only suppress harmonics but also provide reactive power compensation. They are often preferred when an improvement in power factor is also required. Active and passive power filters are the most common approaches used for harmonic cancellation and reactive power compensation.

#### 1.3.2 Passive Power Filters

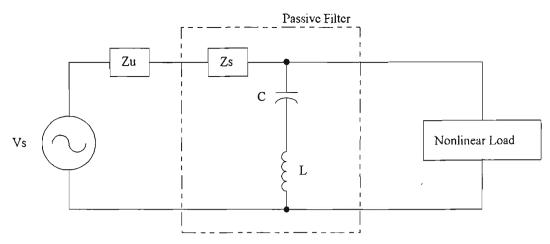

Passive power filters are single frequency filters which absorb individual harmonics. They have been employed to reduce a selected harmonic by tuning the band-pass characteristics of the filter. In time-varying environments an adaptive or automatic tuning feature should be added to these filters [20].

A passive filter as shown in Figure 1.2 consist of a series-resonant inductor-capacitor (LC) circuit tuned to a single frequency. The LC circuit provides a zero impedance path for a selected harmonic current to be filtered. If the line impedance,  $Z_u$ , is low the LC circuit should be used with a series impedance  $Z_s$ . The application of passive tuned filters may create new system resonances which are dependent on specific system conditions.

Figure 1.2: Passive power filter.

Passive filter ratings must be coordinated with reactive power requirements of the loads and it is often difficult to design the filters to avoid leading power factor operation for some load conditions. In other words, they often need to be significantly overrated to account for possible harmonic absorption from the neighbouring power system equipment or from other passive filters [20].

#### 1.3.3 Active Power Filters (APF)

In the recent years there has been considerable interest in the use of active filters for reducing harmonic currents in power supply systems [21-24]. In this section, the general concept of active power filters and their applications will be discussed. A comparison of existing control strategies and hardware characteristics of active power filters is also presented [25].

One of the foremost literature reviews was undertaken by Grady et al [18] covering different APF circuits with emphasis on both time and frequency domain control strategies. Recent research has concentrated on the combination of series and shunt active power filters [26-29]. Power circuits of active power filters and the different series/parallel combinations are investigated in [29].

### 1.3.3.1 Principle of Active Power Filter

To cancel harmonic currents, active power filters inject equal-but-opposite current thereby cancelling the original distortion. Active filters have the advantage of being able to compensate for harmonics without fundamental frequency reactive power concerns. This means that the rating of an active filter can be less than that of a passive filter for the

same nonlinear load. Also an active filter will not introduce system resonances that can move a harmonic problem from one frequency to another.

Classification and comparison of the active power filters can be made from different points of view. Generally, comparison of characteristics of active power filters is summarised in terms of; power system connection, power circuit, and employed control strategy [18, 25].

#### 1.3.4 Power System Connection

The power system connection which determines the type of APF configuration depends on the way in which APF's inverter is connected between source and load. An APF can be connected to the power system in shunt, series and hybrid configurations.

#### 1.3.4.1 Shunt Configurations

A general block diagram of a conventional APF shunt topology is shown in Figure 1.3. In this configuration, the corrective current,  $i_c$ , is injected at the point of common coupling (PCC) to cancel the harmonics contained in the load current  $(i_l)$ . The current,  $i_c$ , can also provide fundamental reactive power compensation for the load if necessary.

Figure 1.3: Basic principle of shunt active power filter.

The shunt APF is controlled in a closed loop to force the source current  $(i_s)$  into a sinusoidal waveform. Two of the main concerns in this configuration are the calculation of the reference input signal  $(i_{ref})$  in steady state and/or transient conditions as well as the response of the system to APF operation. In shunt configurations it is assumed that the load introduces distortions in the form of harmonic currents [29-31].

#### 1.3.4.2 Series Configurations

Figure 1.4 shows a series type of active power filter. In this configuration the active power filter acts as a voltage source in the power system line or as a series filter to prevent the flow of voltage harmonics from the load side to the source.

The voltage drop across the matching transformer of the series filter should be low compared to the nominal line voltage. Thus the power rating of the series active power filter is much smaller than the shunt active filter even though the source currents flow through the matching transformer of the series active power filter. Compared to shunt active power filters, series configurations have some protection difficulties [32].

Figure 1.4: Basic principle of series active power filter.

#### 1.3.4.3 Hybrid configurations

Advances in the area of harmonic reduction have reached the point of combining active and passive filters [29]. The aim is to improve the filter reliability by combining the active power filter performance with the passive filter robustness. Hybrid filters can further reduce the cost of the system compared to pure active power filter approach [25, 33, 34]. In hybrid filter configurations, by improving the compensation characteristics of the passive filter a reduction in the rating of active filter can be achieved [16].

There is a variety of possible active and passive filter combinations [35]. The following combinations can be used:

1. shunt passive and shunt active filters (parallel),

- 2. shunt passive and series active filter,

- 3. shunt passive and active filter in series,

- 4. series active filter with shunt active filter,

- 5. series active filter with shunt passive and active filter in series, and

- 6. shunt Passive filter and two series active filters.

Two configurations are possible for hybrid series active filter based on the position of the series filter. Series filter in the first configuration is placed on the ac side which is referred to as "unified power quality conditioner" [25]. In the second configuration, the series filter is placed on the load side which is referred to as "unified power flow controller" [36].

#### 1.3.5 Control Strategies

The control of active power filters can be categorised into time and frequency domain methods [18, 19, 31]. These will be discussed in the following sections.

#### 1.3.5.1 Time Domain Approaches

Time domain approaches are based on the principle of instantaneous compensation of voltage or current deviation from a sinewave [18, 37]. In this technique, the instantaneous error resulting from the deviation of voltage or current from its reference waveform is used to control the PWM voltage or current source inverters for injection of correcting component into the PCC. The active power filter reference waveform includes the harmonic components of current or voltage as well as the reactive component.

A phase locked loop (PLL) tracks the fundamental frequency component and provides a timing reference for the controls. The main advantage of time-domain techniques is the fast response to changes in the load harmonic current. The computational burden of time-domain approaches are minimal [18].

The instantaneous power transformation is a popular time-domain active power-filter control strategy [23, 38]. In this method a three-phase power system voltage, current and instantaneous power are transformed into well known  $\alpha$ - $\beta$ -0 components [39] and

the instantaneous active, reactive and harmonic powers are separated where the active power filter compensates for the instantaneous reactive power. The instantaneous reactive power is quite different in definition to conventional reactive power based on the average value concept [23].

In time domain approaches neither individual harmonics can be separately compensated nor any weighting could be applied for different harmonic components.

#### 1.3.5.2 Predetermined Harmonic Cancellation

As in the case of tuned passive filters, predetermined harmonics can be chosen for compensation using active power filters [18, 22]. It is assumed that the load current harmonic components are stationary and known in advance. The compensating reference current waveform is synthesised from the predetermined harmonic components [40, 41]. It is possible to reduce the specific harmonic with a desired level of compensation leading to reduction in the power rating of the active power filter. The main disadvantage of this method is the high computational burden as the order of the highest harmonic to be compensated increases [41].

A PWM switching strategy for a full-bridge inverter has been proposed [42, 43] which can be used for predetermined harmonic compensation. This switching strategy can reduce the total harmonic distortion of the inverter current output while minimising the switching losses when hybrid switching sequences are employed. A detailed discussion on this PWM technique will be presented in Chapter 2.

#### 1.3.5.3 Frequency Domain Approaches

In frequency domain approaches, the frequency components of the load current are identified using frequency analysis such as the Fourier or Wavelet transforms [44]. These frequency components are used to determine the harmonic compensation reference waveform.

The frequency domain analysis of voltage or current distortion gives the flexibility of using different configurations and circuits for each harmonic [35]. For instance, to compensate the current harmonics of an AC adjustable speed drive (ASD) passive filters

can be installed for the fifth harmonic which is the dominant harmonic component and a single active filter to compensate all the other harmonics and/or interharmonics.

The most commonly used tool for frequency domain analysis is the fast Fourier transform (FFT). The individual harmonic components in the load current are retrieved by performing a sliding FFT on the sampled load current waveform and then reproducing a compensating current waveform that has the exact harmonic components with the opposite phase angle. The main disadvantage of this technique is the high computational burden when compared to the time domain techniques.

#### 1.4 THESIS OBJECTIVES AND OUTLINE

The objective of the work presented in this thesis is to develop control strategies that could be applied for harmonic reduction in the load and the power system. The work includes two different approaches for harmonic reduction, a new pulsewidth modulation technique and an adaptive control strategy for active power filtering. The proposed control strategy for active power filter employs adaptive online harmonic estimation together with a selective harmonic compensation scheme which is a compromise solution between fulfilling the requirements of a harmonic standard and the cost of equipment for power quality improvement.

### 1.4.1 Pulsewidth Modulation (PWM)

A novel PWM switching strategy using an equal area PWM (EAPWM) technique is developed which is suitable for full-bridge inverter applications. The objective of the new switching strategy is to minimise both the total harmonic distortion and low order harmonics in full-bridge inverter output. In addition, a hybrid switching sequence is developed for the proposed EAPWM technique such that further reduction in switching losses can be achieved.

#### 1.4.2 Adaptive Active Power Filter (AAPF)

A novel control strategy suitable for a shunt active power filter is proposed. This control strategy includes on-line phase/frequency tracking, a filter bank based harmonic estimation and a selective harmonic compensation scheme. The motivation behind the

proposed control strategy is a reduction in active filter power rating while keeping the minimum requirements for harmonic reduction as specified by harmonic standards.

#### 1.4.2.1 Harmonic Estimation

Selective harmonic cancellation requires an accurate on-line measurement of individual harmonics. This measurement should be fast and robust to transients, noise and time-varying phenomena such as variation in fundamental frequency and magnitude and the changes in the load current.

In order to retrieve individual harmonics on-line, a resonator based infinite impulse response (IIR) filter bank (FB) has been proposed. The parallel structure of this filter enables the desired harmonic order to be obtained while keeping the computational burden low. In this structure, each filter in the filter bank retrieves the specific harmonic.

To determine whether the requirements of a harmonic standard are fulfilled, the magnitude of each harmonic is compared against the recommended level. If the harmonic magnitude exceeds the recommended level or has been selected for full compensation, it will be considered in the harmonic reduction process.

#### 1.4.2.2 Phase and Frequency Tracking

To adaptively change the parameters of the filter bank according to the time-varying parameters of the power system or compensation process, a frequency demodulation (FDM) technique for on-line tracking of the power system voltage phase and frequency has been employed. In this technique, any frequency deviation of the power system can be identified and applied for filter bank parameterisation.

The reactive power compensation for power factor correction has been incorporated into the harmonic compensation schemes. The power factor of the load is calculated using the estimated phase of the fundamental current with respect to the supply voltage phase.

#### 1.4.2.3 Selective and Partial Harmonic Compensation Schemes

Different harmonic reduction schemes are proposed to generate the compensating reference current waveform for the active power filter. The different approaches are distinguished by how the reference current waveform is derived from the estimated

harmonic components and fundamental reactive power. The level of harmonic and reactive power compensation can be intelligently selected to meet the requirements set by harmonic standards.

A reduction in active filter power rating can be achieved by employing a selective harmonic compensation scheme. The way to use this concept is to provide only enough compensation power so that the supply harmonic current levels are within the recommended levels as set by the harmonic standards.

#### 1.4.3 Contributions of the Thesis

A number of contributions have been made as a result of this work. A brief summary of each contribution is as follows:

#### 1.4.3.1 New PWM Switching Strategy

A new PWM switching strategy for full-bridge inverters has been proposed which gives a lower harmonic distortion compared to conventional switching strategies [42, 43]. The performance of the proposed switching technique and three other conventional PWM switching techniques have been evaluated for synthesising sinusoidal waveforms. Application of the proposed PWM switching technique in active power filtering for predetermined harmonic cancellation has also been evaluated.

#### 1.4.3.2 Harmonic Estimation

A resonator based IIR filter bank has been proposed for on-line power system harmonic estimation. The sliding technique for on-line measurement of the harmonic magnitude and phase is introduced for active power filter applications. Also a harmonic phase prediction technique is proposed to compensate for the phase error due to the delay in the data acquisition and processing.

Due to possible frequency variations in the power system an instantaneous phase and frequency tracking method is required. The tracking accuracy of two methods, FM demodulation and adaptive IIR filtering techniques were evaluated and subsequently the FM demodulation technique was chosen because of its preferred characteristics [45].

#### 1.4.3.3 Adaptive Active Power Filter

A laboratory prototype of the active power filter circuit has been implemented. Software modules were developed for the proposed control strategy and were implemented on a digital signal processor (DSP).

By employing the proposed harmonic reduction schemes one is able to control the level of harmonic current compensation together with power factor correction. The proposed control strategy enables a reduction in the power rating of an active power filter by selecting specified harmonics for partial or full compensation.

#### 1.4.4 Thesis Outline

Chapter 2 reviews the principles and software implementation of the proposed switching strategy for a full-bridge inverter along with a comparison of existing switching strategies including Natural, Uniform and Equal Sampling Techniques.

The concept of the filter bank based harmonic estimation is described in Chapter 3. An on-line frequency tracking methodology is proposed for the parameterisation of filter bank design. It includes power system voltage phase and frequency tracking. The simulation results for performance evaluation of the proposed frequency and harmonic estimation technique are presented. A comparison of the simulation results for the filter bank based harmonic estimation and the short term Fourier transforms (STFT) technique is presented.

Chapter 4 discusses issues regarding the hardware design of adaptive active power filter and software implementation of harmonic estimation and PWM techniques on the DSP board.

The experimental results of the entire system including the proposed PWM technique and its performance under different conditions are presented in Chapter 5. Experimental results for steady state and transient conditions are given to evaluate the performance of the proposed control strategy for active power filters. The results for different harmonic compensation schemes are also presented and discussed.

Chapter 6 concludes the thesis and outlines some recommendations for future research work.

## **CHAPTER**

# 2.

## EQUAL AREA BASED PWM TECHNIQUE

#### 2.1 Introduction

This chapter is concerned with the development of a new pulse-width modulation (PWM) switching strategy for general inverter based applications. The proposed PWM switching strategy described herein is developed to give low harmonic voltage distortion without leading to significant switching losses.

In most pulsewidth modulation (PWM) switching environments, such as voltage source inverters (VSI), minimisation of unwanted harmonics implies a low harmonic distortion. Attempts to develop more sophisticated PWM switching strategies to obtain better (ie. minimal harmonic distortion) variable speed drive performance have recently been reported [46]. Existing PWM switching strategies have been designed to eliminate selected harmonics [47], minimise harmonic losses and reduce the harmonic distortion [48]. To generate such a PWM pattern, a set of complex equations associated with these PWM switching strategies require off-line solution [49]. On-line implementation of these switching strategies make extensive use of look-up tables (LUT) and significant off-line pre-calculation and computing resources [50].

The harmonic content of the inverter output waveform and switching losses are the principal concerns in most applications and thus the aim is to minimise the harmonic distortion and switching losses.

For medium and high power level inverters where the maximum switching frequency is restricted by switching losses, a PWM technique with a lower switching frequency is preferred. The idea is to optimise (ie minimise) both switching losses and total harmonic distortion. This Chapter is concerned with the development of a PWM switching strategy for full-bridge inverters with a low switching frequency which gives improved performance in comparison to existing switching strategies.

## 2.2 CONVENTIONAL PWM TECHNIQUES

## 2.2.1 Natural Sampling PWM Technique

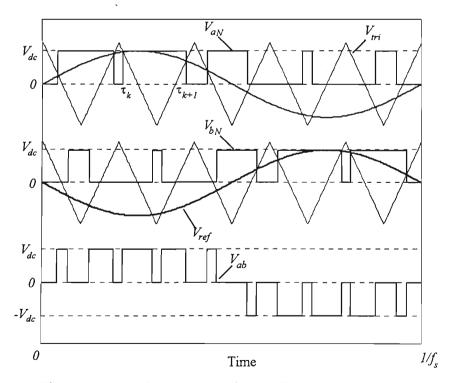

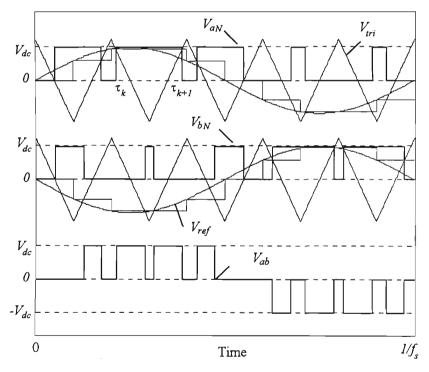

The conventional PWM technique for generating the switching pattern for a full-bridge inverter is referred to as the natural sampling PWM technique [47, 51]. The PWM pattern for each leg of the inverter is determined by intersections between a triangular voltage waveform,  $V_{tri}$ , and a sinusoidal reference waveform  $v_{ref}(t)$ , as shown in Figure 2.1, as follows:

$$v_{ref}(t) = V_m \sin(\omega_0 t), \quad \omega_0 = 2\pi f_0 \tag{2.1}$$

where  $V_m$  is the peak amplitude of desired output voltage  $v_{ref}(t)$  and  $V_{tri}$  is the peak amplitude of the triangular waveform with a frequency of  $f_{tri} = 1/T_{tri}$ .

Figure 2.1: Natural PWM technique.

Figure 2.2 shows the PWM pattern for each leg of full-bridge inverter shown in Figure 2.3 for a frequency ratio p=10, and a modulation depth M=0.8, where the frequency ratio p is defined as:

$$p = \frac{f_{tri}}{f_0} \tag{2.2}$$

where  $f_{tri}$  is the frequency of the triangular waveform and  $f_o$  is the reference waveform frequency. The modulation depth is defined as:

$$M = \frac{V_m}{V_{tri}} = modulation \ depth$$

(2.3)

The  $k^{th}$  pulsewidth  $(\tau_{k+1} - \tau_k)$  in the natural sampling technique is proportional to the amplitude of the modulated signal at the time of intersection which is defined by the transcendental equation [51]:

$$\tau_k = t_{k+1} - t_k = \frac{T_{tri}}{2} \left[ 1 + \frac{M}{2} (\sin \omega t_1 + \sin \omega t_2) \right]$$

(2.4)

Equation (2.4) can be solved only numerically [51]. The analog processes of natural sampling technique can be implemented on a digital platform. However it requires a large number of samples of the reference waveform and imposes extensive computational burden.

Figure 2.2: Unipolar natural sampling PWM patterns.

In the unipolar natural sampling (UPNS) PWM technique, each switching leg of the full-bridge inverter (Figure 2.3) is driven by its own PWM pattern [52]. As shown in

Figure 2.2, the reference waveform for switching of the second leg is  $180^{\circ}$  out-of-phase. Therefore, the output voltage changes between zero and  $+V_{dc}$  or between zero and  $-V_{dc}$  voltage levels where  $V_{dc}$  is the voltage of the DC link of the inverter.

Figure 2.3: Full-bridge inverter.

## 2.2.2 Regular Sampling PWM Technique

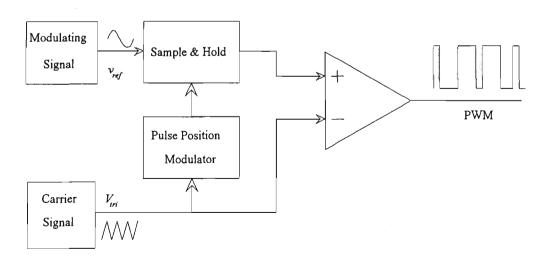

Regular PWM sampling techniques, with and without third-harmonic distortion, has been adopted to reduce the harmonic distortion and facilitate implementation on a digital platform [51, 53]. Figure 2.4 shows the circuit block diagram for the regular sampling PWM technique. The reference waveform is sampled and then compared with the triangular carrier signal to generate the PWM switching pattern.

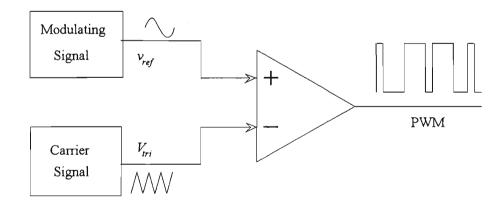

Figure 2.4: Regular sampling PWM technique.

Figure 2.5 shows the PWM pattern for unipolar regular asymmetric sampling (UPRAS) where the reference waveform is sampled at twice the carrier frequency. The  $k^{th}$  pulsewidth,  $\tau_k$ , is given by:

$$\tau_k = \frac{T_{tri}}{2} \left[ 1 + \frac{M}{2} (\sin \omega t_k + \sin \omega t_{k+1}) \right]$$

(2.5)

where

$$t_{k+1} = t_k + \frac{T_{tri}}{2} (2.6)$$

The main advantage of this approach over the UPNS PWM technique is that the information required to be stored for on-line applications is reduced to the number of levels at the output of the sample and hold block of Figure 2.4, which is equal p [54].

Figure 2.5: Unipolar regular asymmetric sampling PWM pattern.

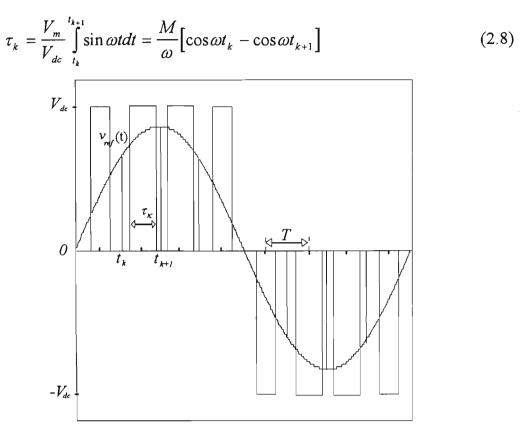

## 2.2.3 Equal Sampling PWM Technique (EST)